此为一些Cadence ic618 EDA 软件操作说明记录,以防某些原因会忘记,同时希望可以帮助到其他的IC设计工程师。

1.LVS Debug经验

电路中存在dummy等一些用于版图匹配但无实际意义的MOS管等器件,在LVS时需要在LVS option中supply 找到Filter Unused Device Option 来屏蔽这些虚拟管

之前的 项目 选择屏蔽:AB AC RB RC ZB

Tips:在LVS纠错时,为了能看清layout走线,经常使用Cadence工具栏中Connectivity - Mark来标记走线的连接情况。

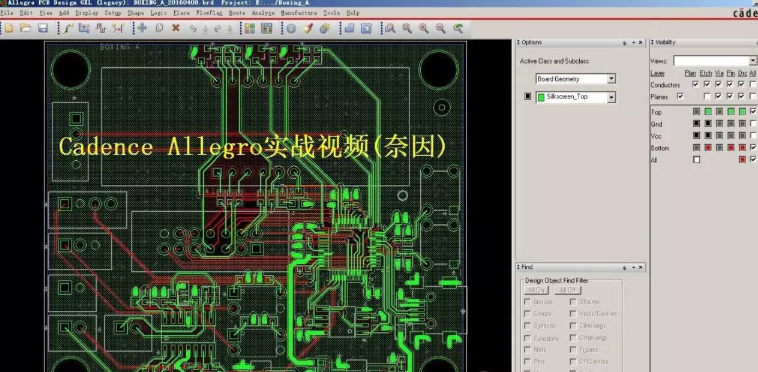

2. 电路设计 之后的版图布局

根据需求设计完相应的电路之后,这并不代表着万事大吉,对模拟设计工作者来说,糟糕的器件尺寸设计会引来版图设计工作者的问候,因此我们需要在交付设计之前,自身评估器件摆放与器件尺寸以及版图利用率。

通过工具栏中的 Launch - Layout XL 之后点击左下角的Generate All From Source  ,可以自动调用电路图中模块的版图,在弹出的框中 PR Boundary 可以标定版图利用率与拟版图面积,这是为了估算版图器件摆放的工具。

,可以自动调用电路图中模块的版图,在弹出的框中 PR Boundary 可以标定版图利用率与拟版图面积,这是为了估算版图器件摆放的工具。

3.内部节点设置初始状态(Deepprobe)

在一些需要设置初始状态才能启动的电路中,在前仿时设置初始状态会比较方便ADE L- Simulation - Convergence Aids Node set/ IC。

但是在后仿时,电路模块被替换为版图数据,无法通过正常设置电路时设置初态,有两种方法:

(1)通过修改版图,增加初态点的PIN来设置。

(2)使用analogLIB中的Deepprobe,通过语法 Instance.instance.netxx,设置特定点的初始状态。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删