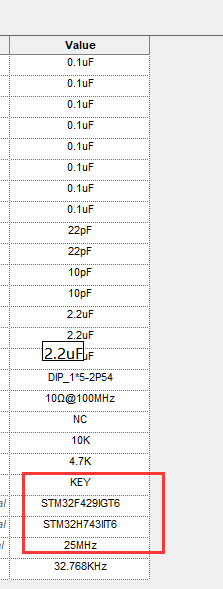

接着第三天的内容已经将原理图,PCB封装都就绪,各元器件的Value以及PCB FootPoint都已经配置好了。

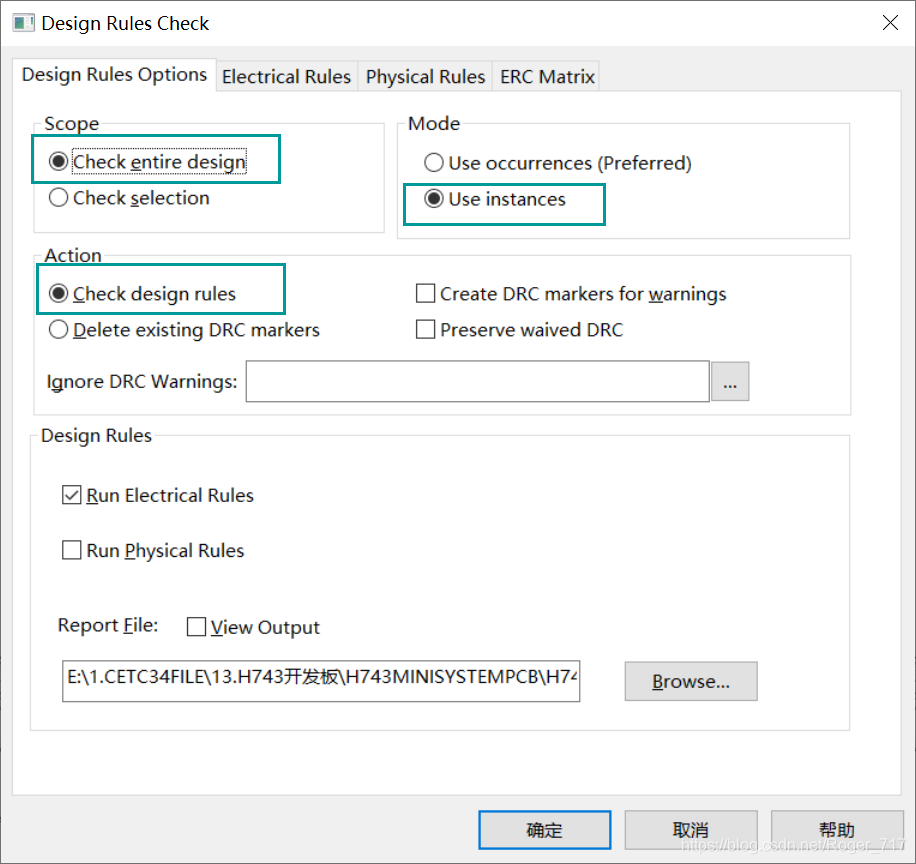

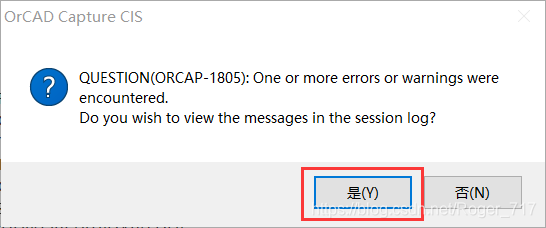

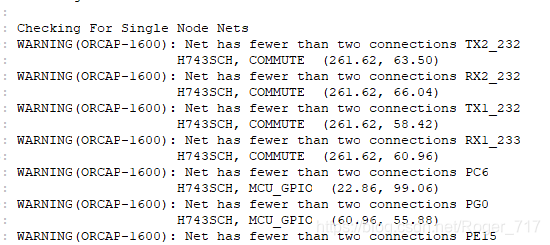

原理图设计完成后一定要进行DRC验证,确保原理图设计没有问题,再进行后续的PCB设计流程,主要是电气规则办法。

选中 根目录 ,找到Tools -> Design Rules Check

这只是提醒你有个网络只有一个端口、也就是说他没有连接到别处、这个很常见、不会影响生成网表。

网络表是原理图和PCB之间的桥梁,PCB通过导入原理图生成的网表,才能正确的进行设计。

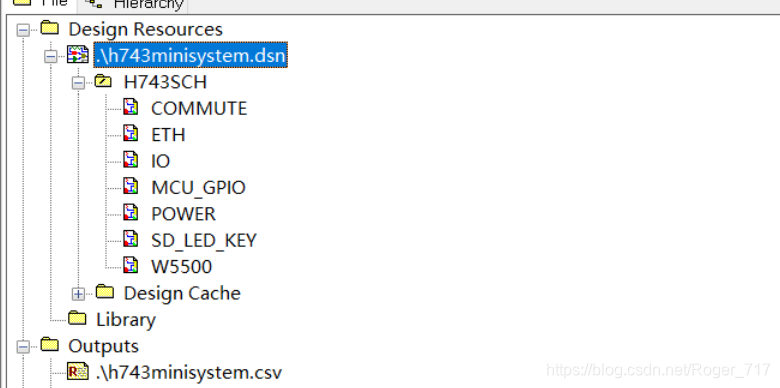

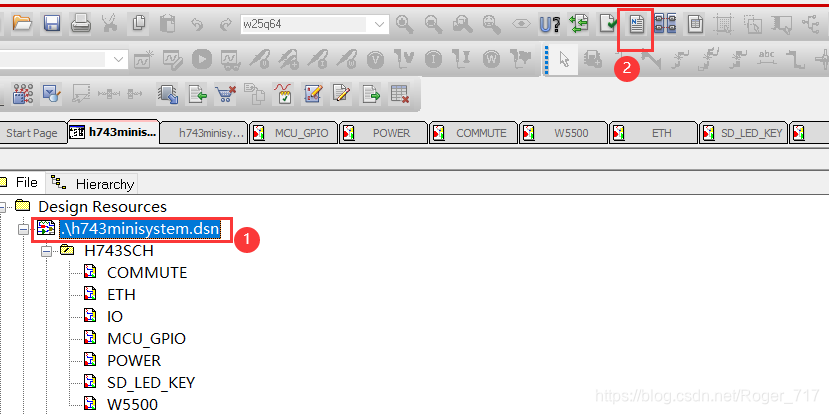

选中根目录:

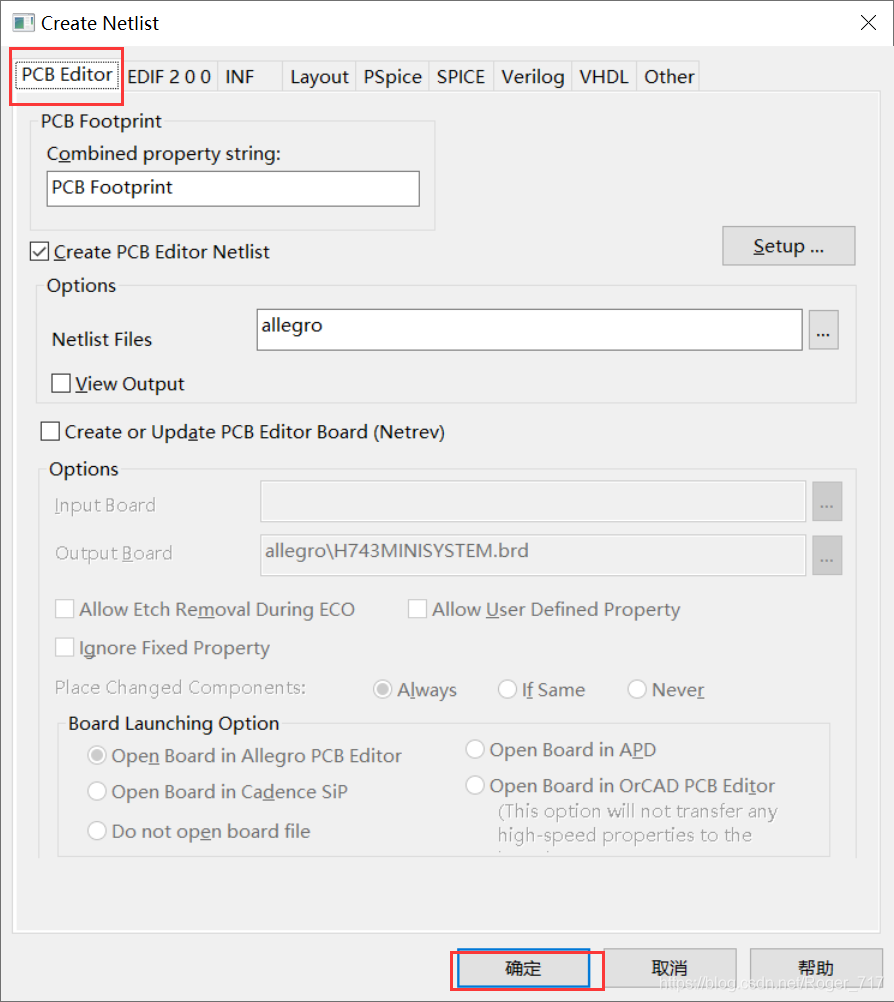

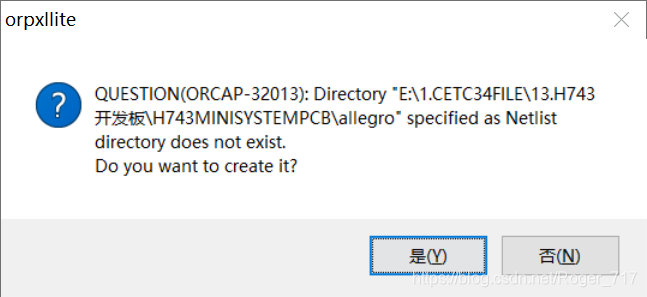

选择 Tools -> Create Netlist

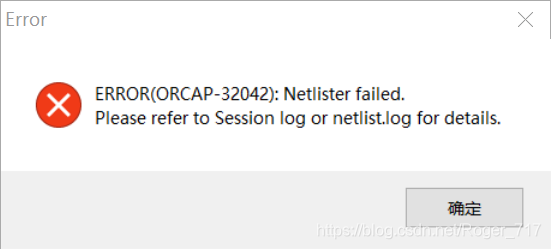

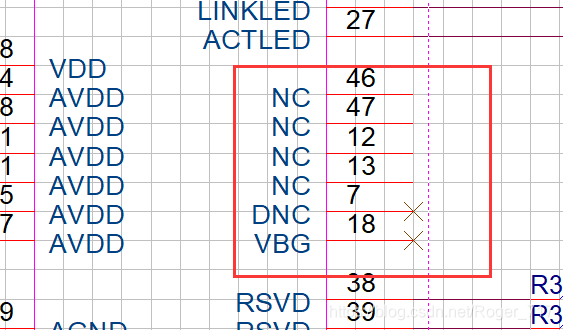

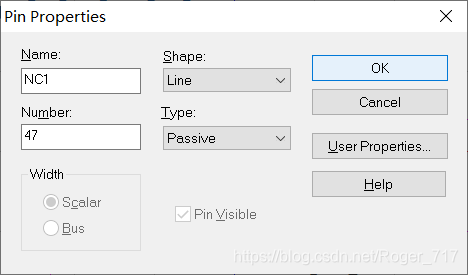

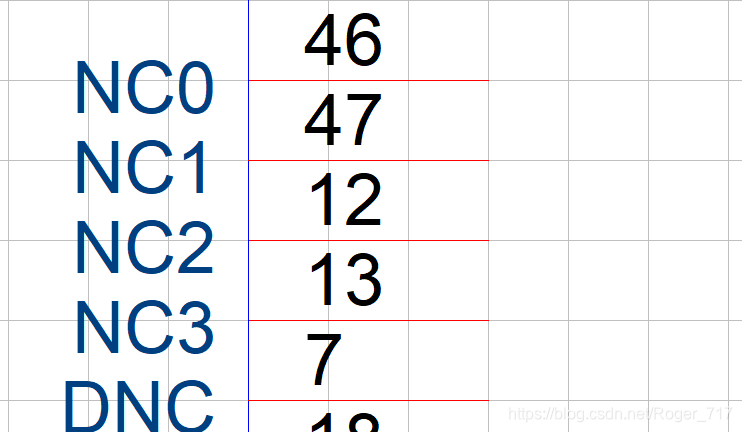

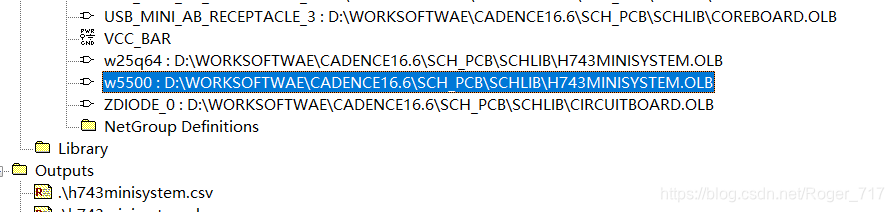

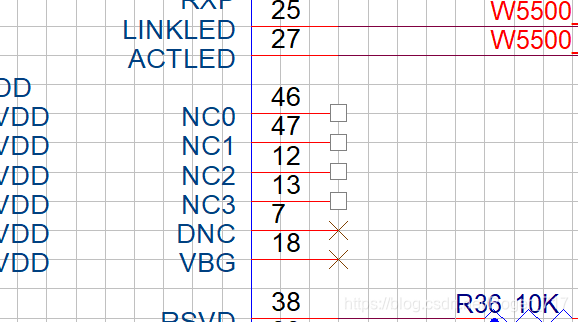

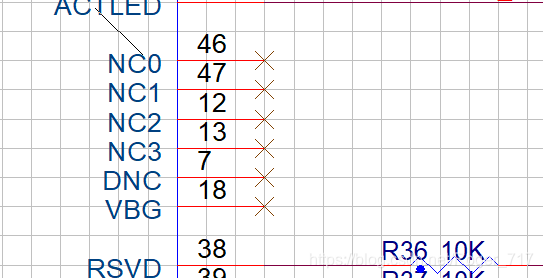

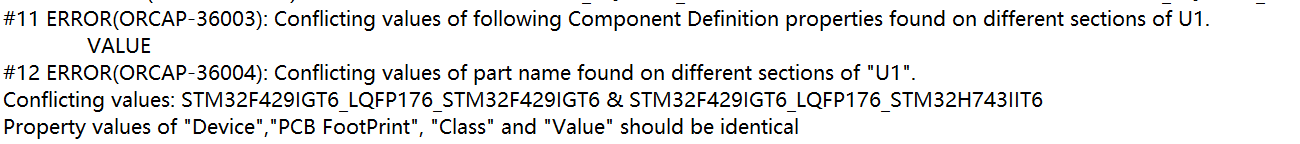

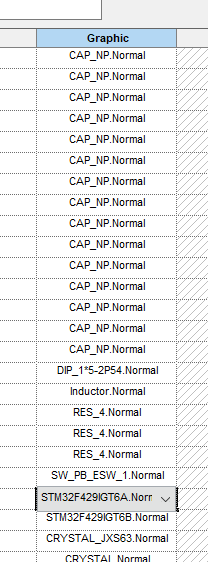

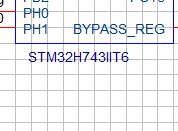

出现了问题,我们找到文件夹netlist就会发现报错的原因是因为定义引脚出现了问题,我们修改一下该封装。

保存好原理图将其更新一下

改成一样的之后再生成网表就正确了。

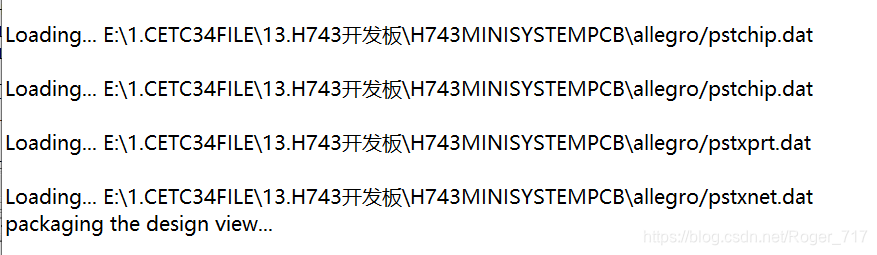

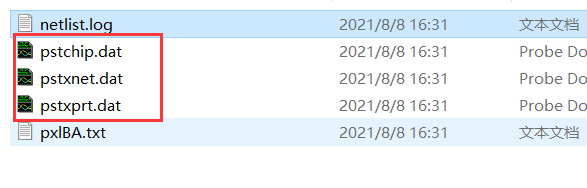

生成如下三个网表。

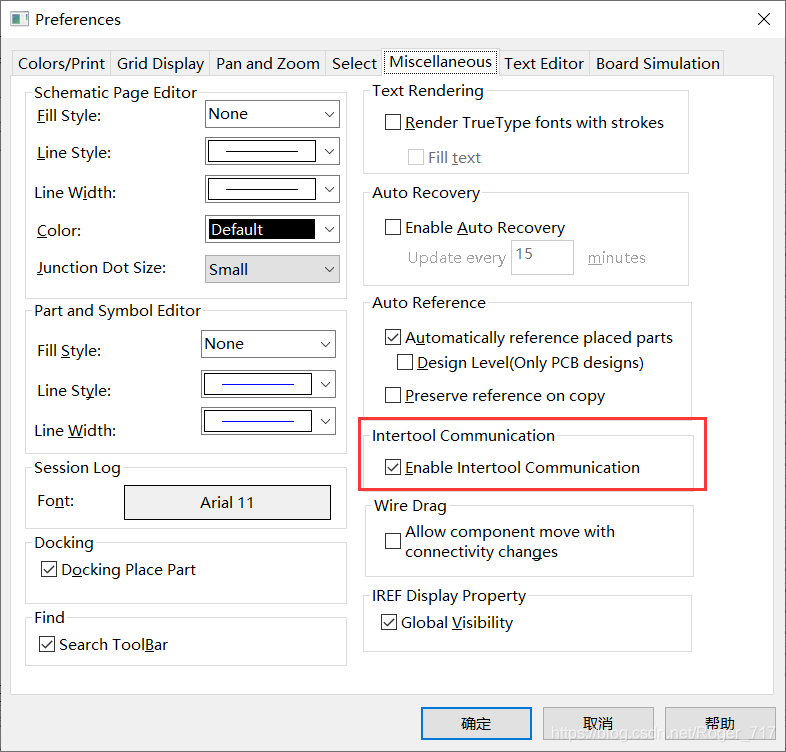

options -> Preference ->Miscellaneous,将下面的勾选。

o

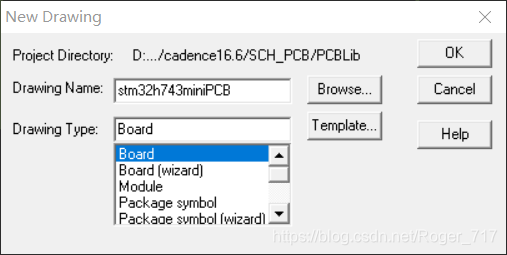

打开这个 软件。点击File -> new

软件。点击File -> new

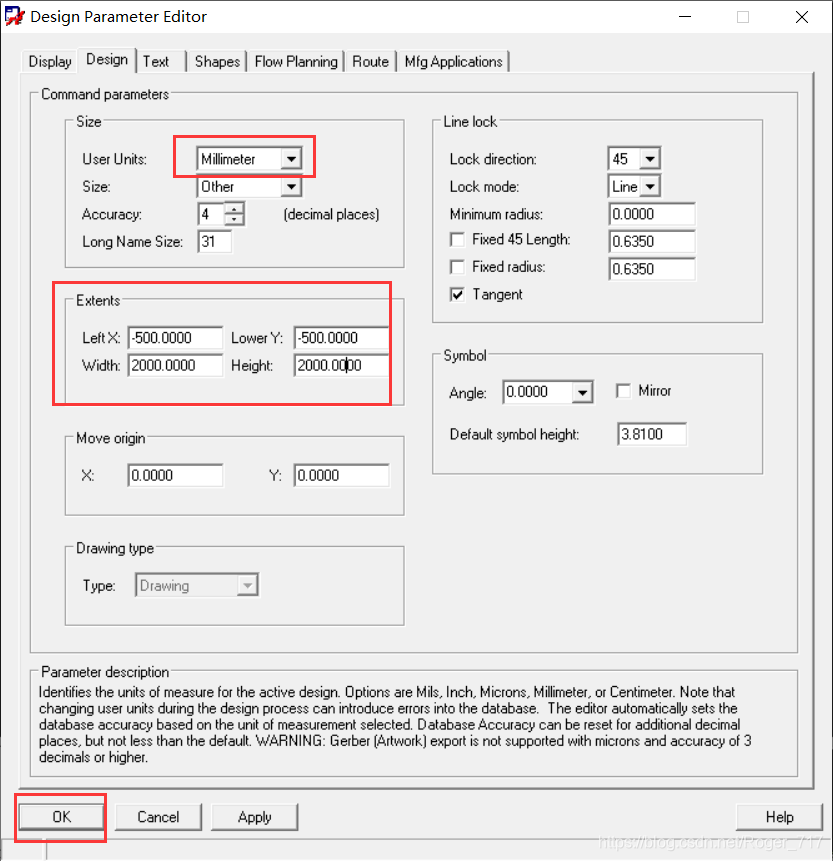

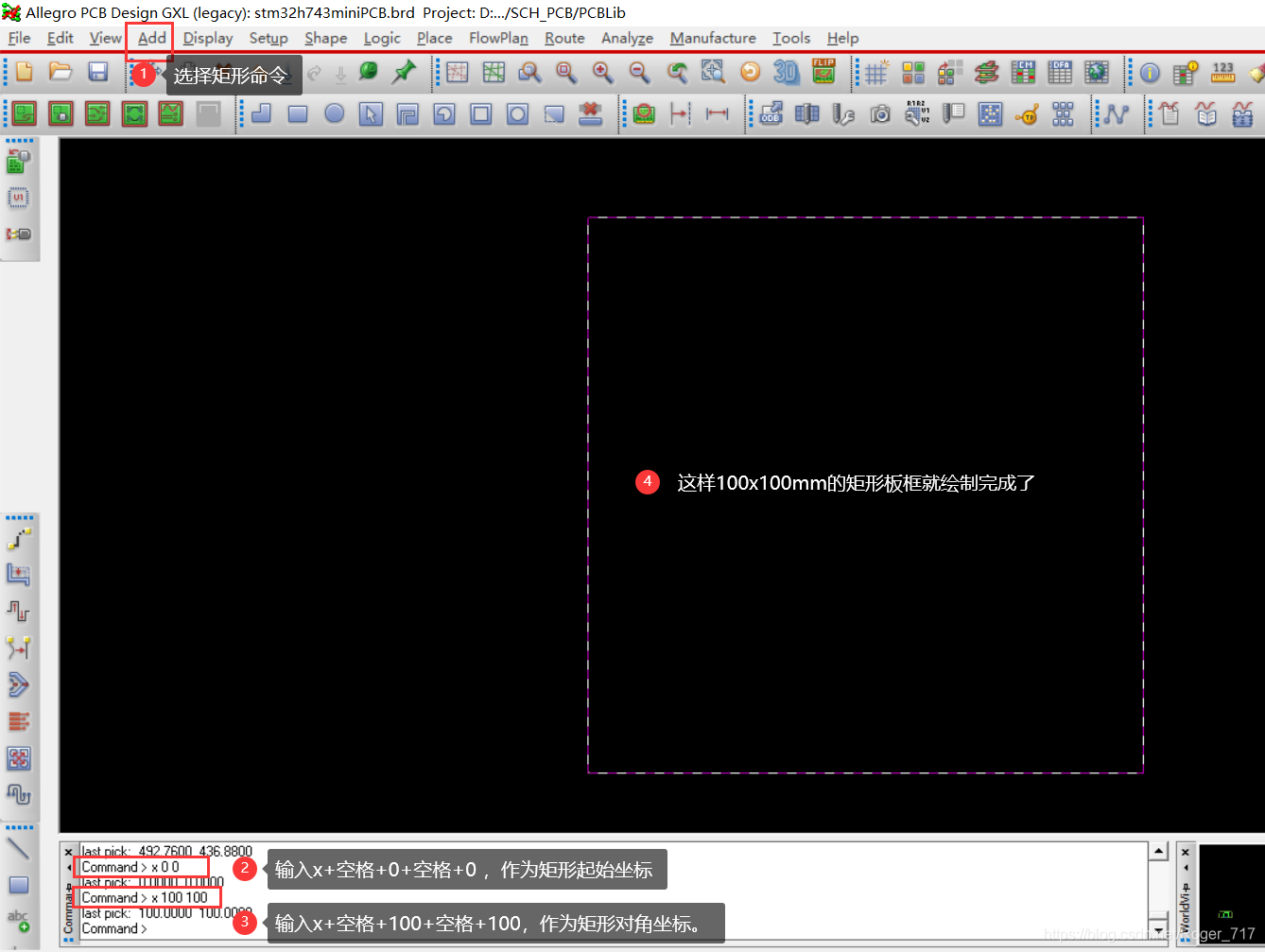

之后进行基础配置,栅格显示,尺寸单位显示等。-500,-500 是左下角坐标。

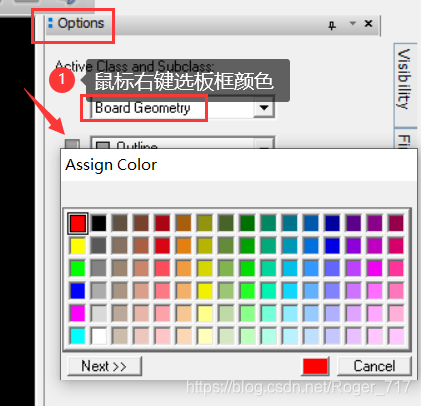

该板框属性是在OutLine Shapes.

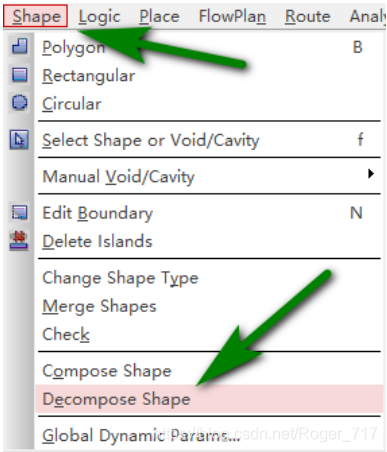

我们这一步所作的长方形为一个形状,并不是line属性,倒角并不成功,因为倒角功能需要对line属性的线条有效,此时需要将shape属性打散,菜单Shape>Decompose Shape,选中这个长方形,即可改变属性。

选中执行Decompose Shape命令,把铜片属性的板框变成线属性线的板框。

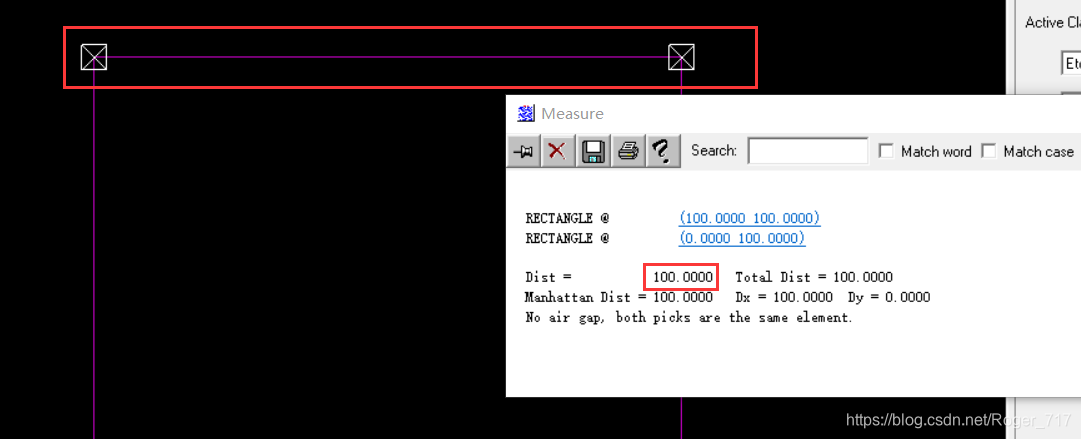

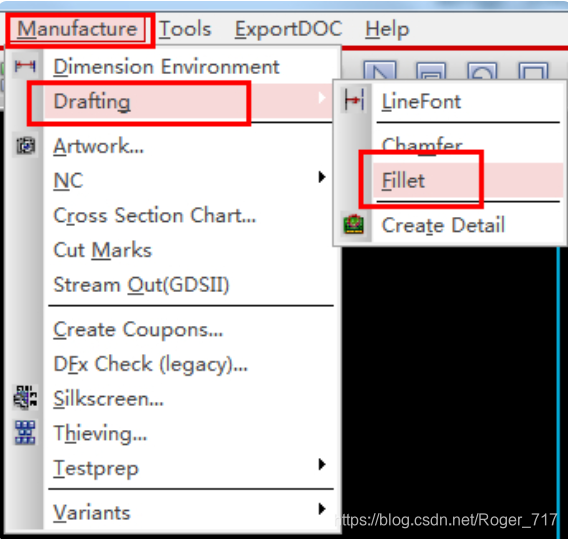

Allegro PCB设计中板框圆弧过程:执行manufacture下面的Drafting - fillet命令,如图所示:

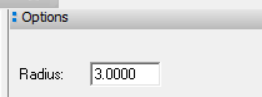

选择完倒角半径之后,用十字鼠标点击俩个边框,两个边框之间的倒角就会生成了。

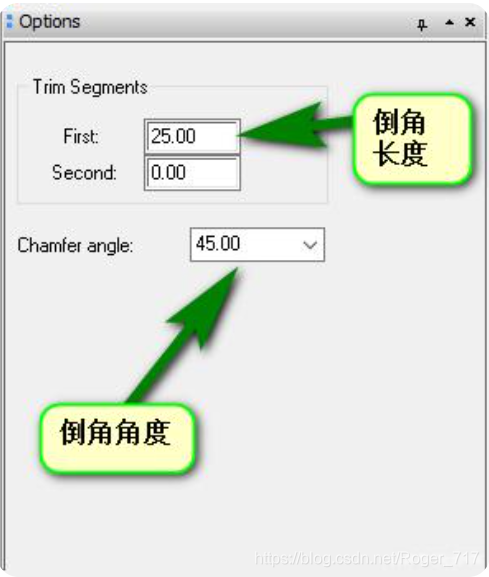

倒斜角方法:选菜单栏Manufacture——Drafting——Chamfer,然后在Options侧边栏填写倒角长度和倒角角度。

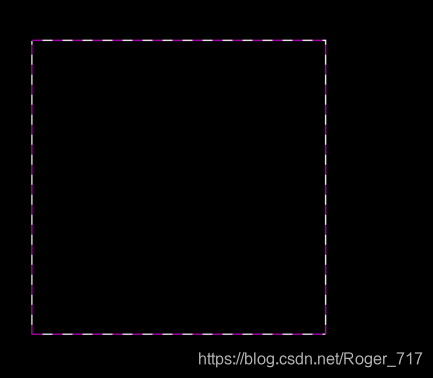

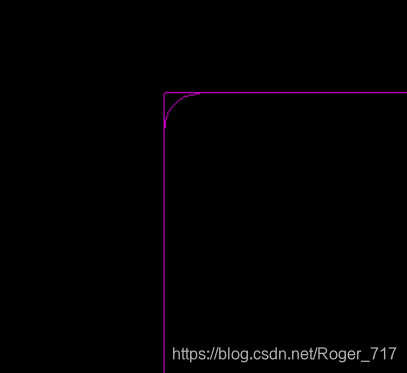

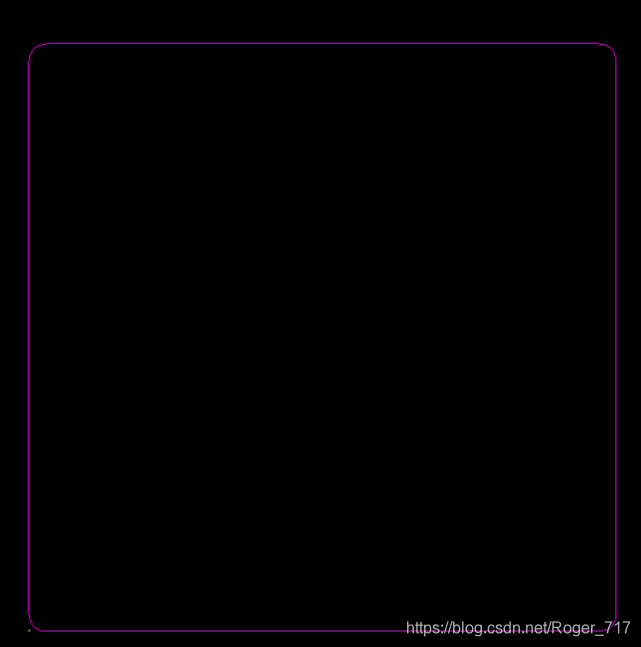

倒角完成后,因为decompose shape后的板框属性已经不是板框层,如下图。同时之前的正方形删掉,删除之后如下。

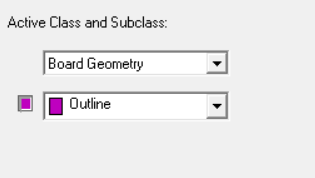

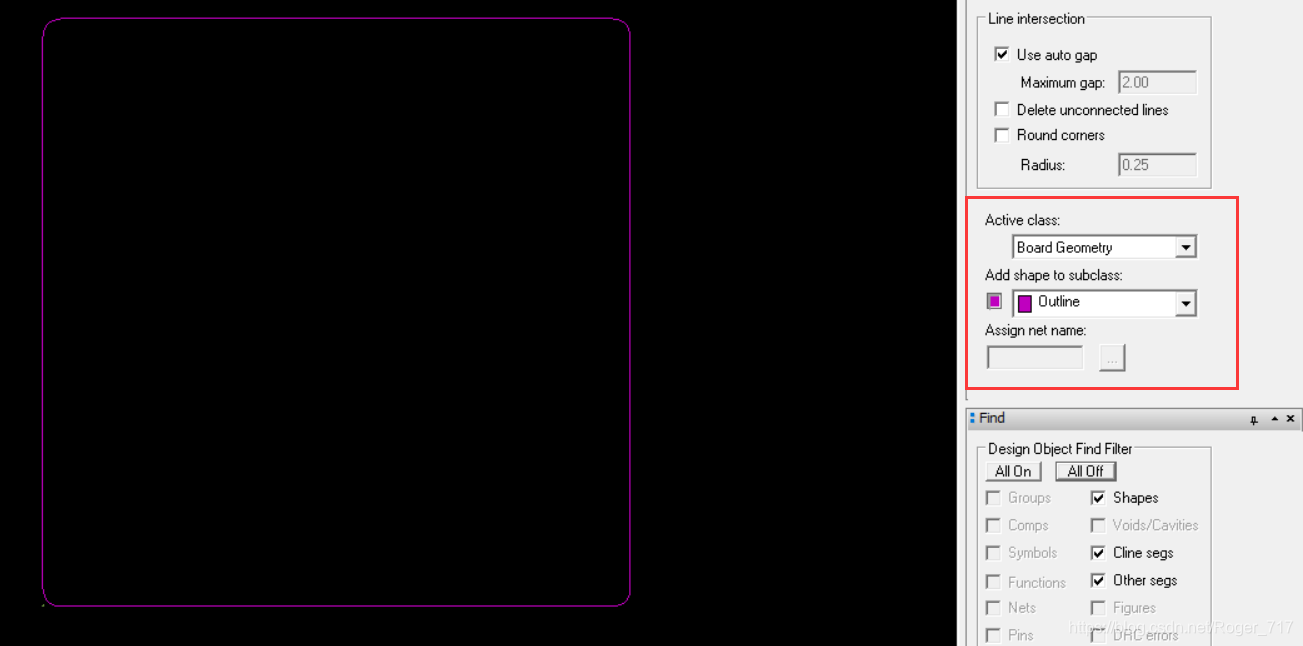

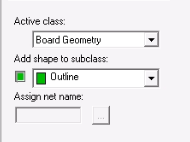

所以我们需要再对修改后的板框再进行compose shape。菜单Shape>Compose Shape,使之再次成为一个shape属性。注意在Options里面要选择我们需要的板框层,如果是板子外形,可以使用Board Geometry>Outline,如果是做封装,我选择使用Package Geometry>Silkscreen_Top。然后选中倒角后的边框,即可改变板层属性。

网表是原理图和PCB连接的媒介,将原理图的电气连接关系及封装类型信息导入PCB中,实现逻辑与物理连接。

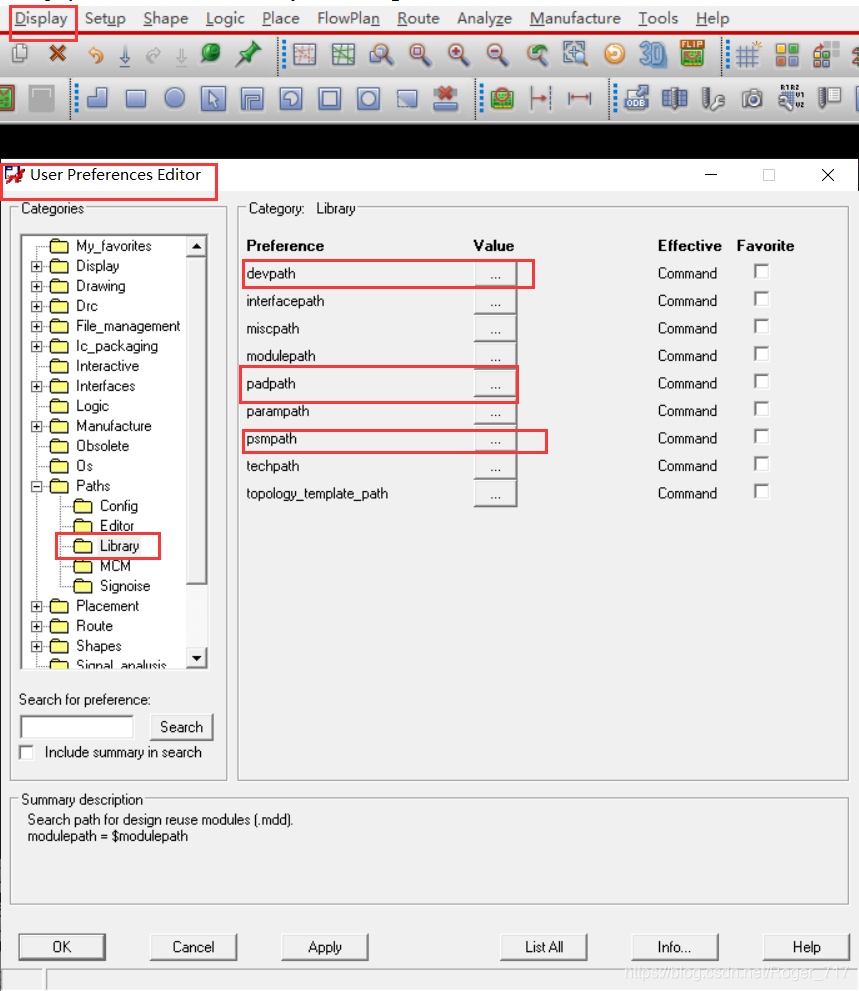

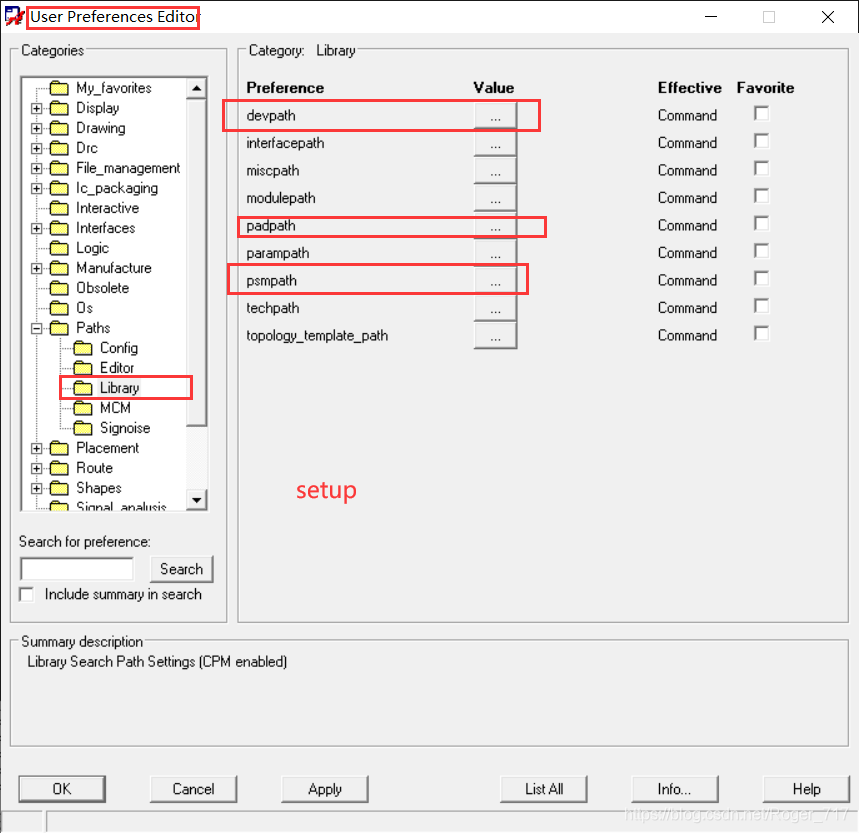

设置封装库路径:

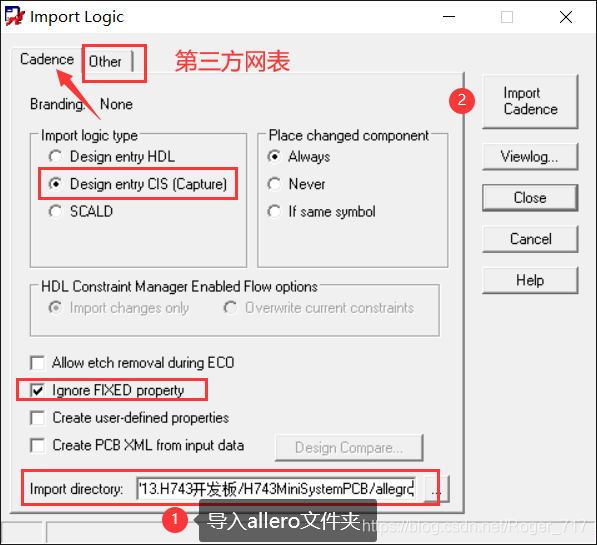

导入第一方网表可以不用封装先导入网表,第三方导入需要先导入封装,不然报错。

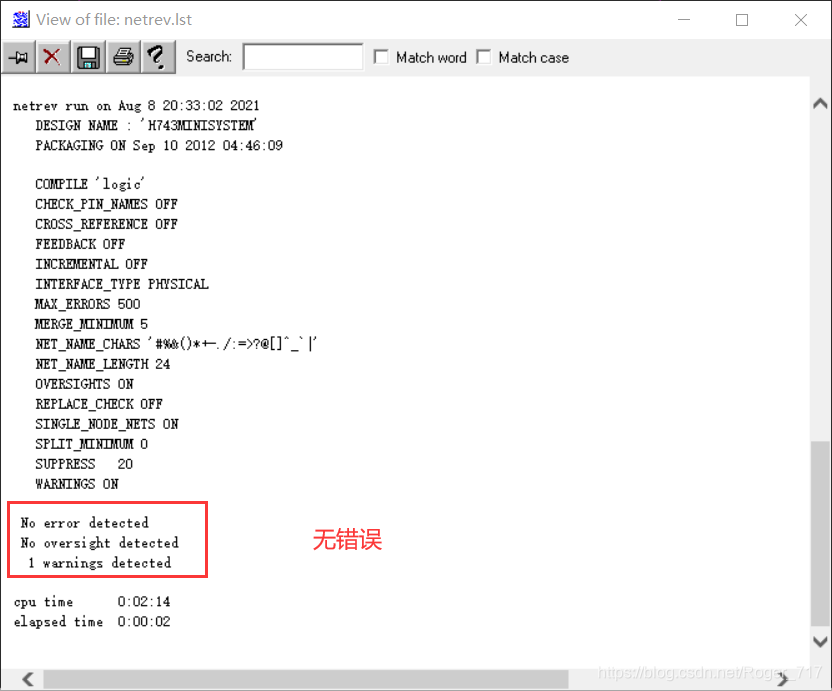

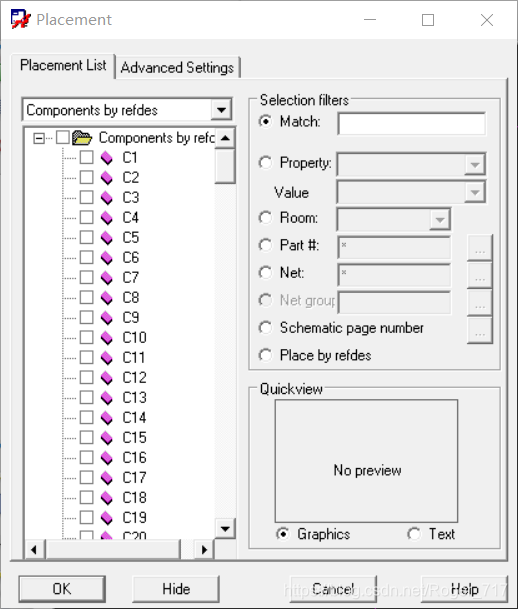

导入之后查看Place -> Manually 可以看到有元器件导入。

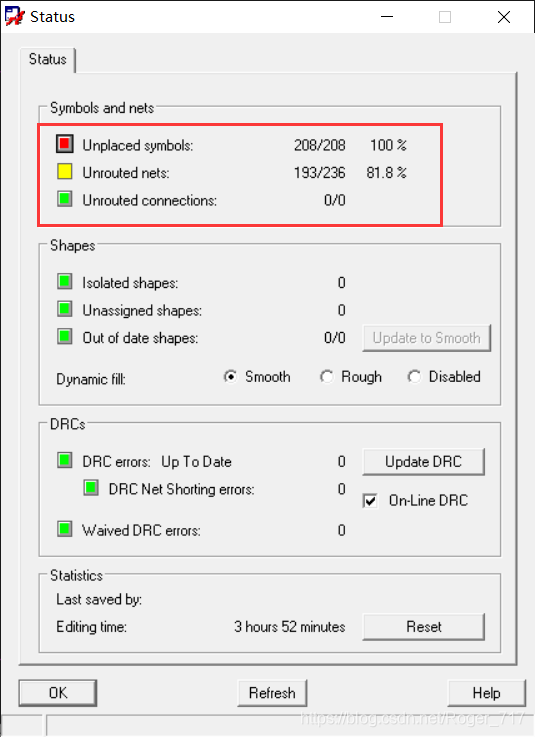

或者查看Display -> Status可以看见未导入的器件数目,网络81.8%是因为有的网络没有使用。

放置路径之前要指定库路径;

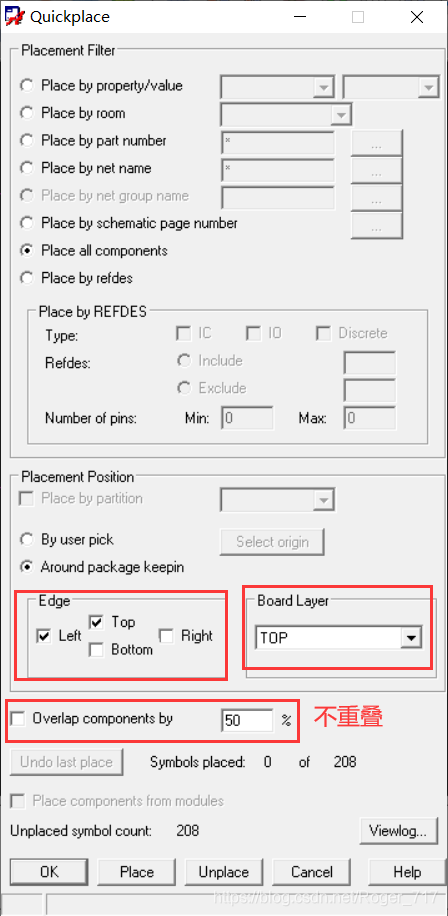

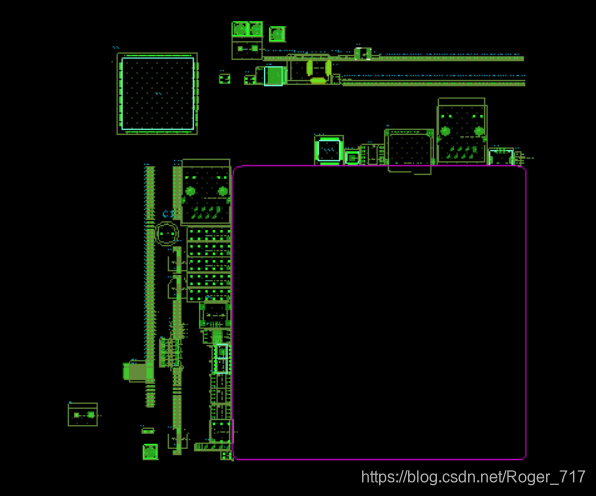

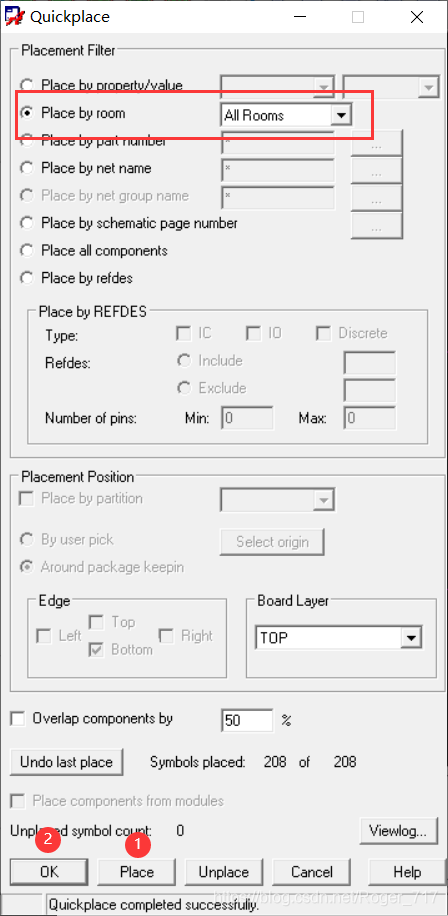

Place -> Quickplace

然后点击Place

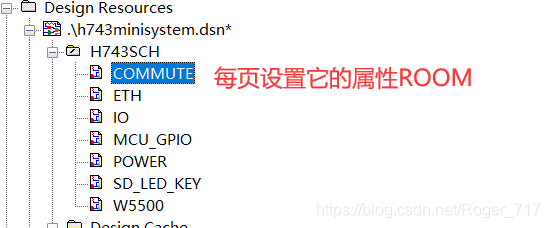

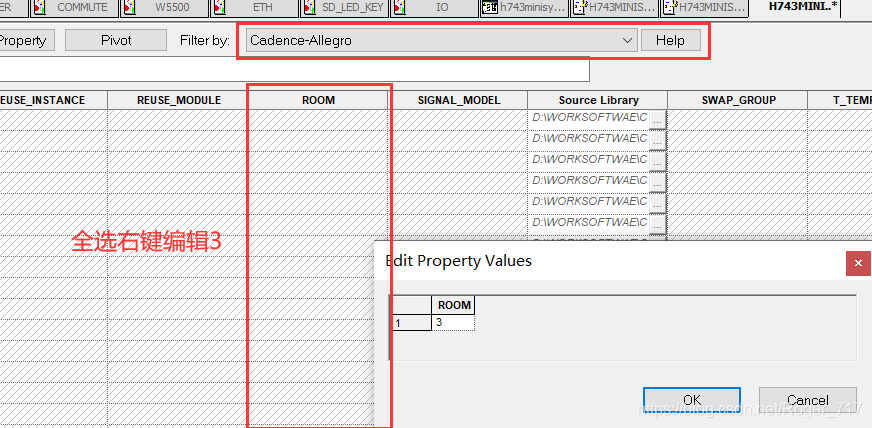

在原理图绘制软件

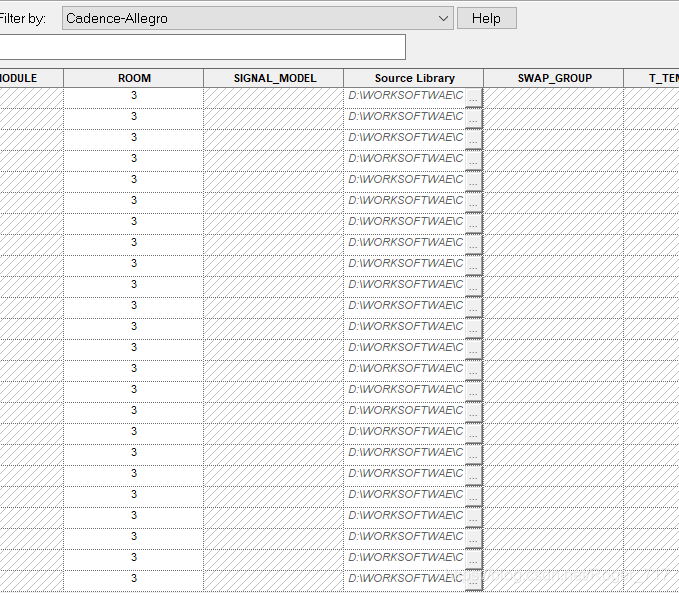

其它页同样设置,设置完成后重新导出网表。

生成后重新导入PCB中。

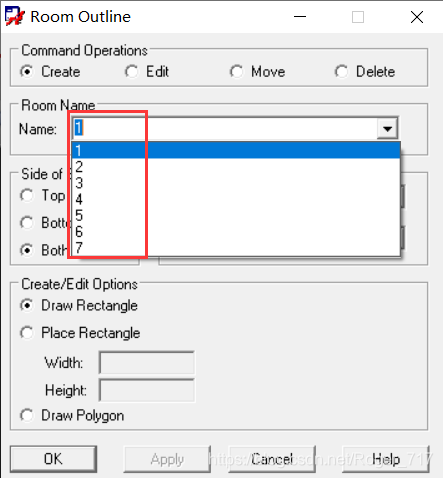

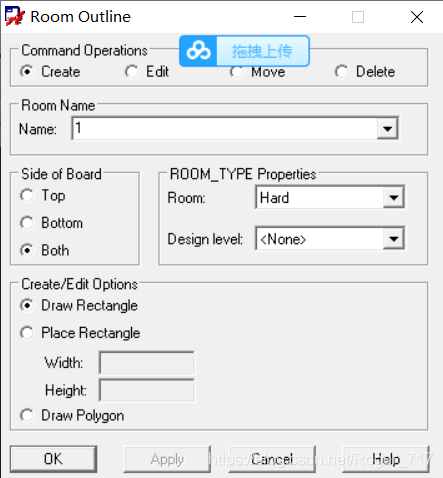

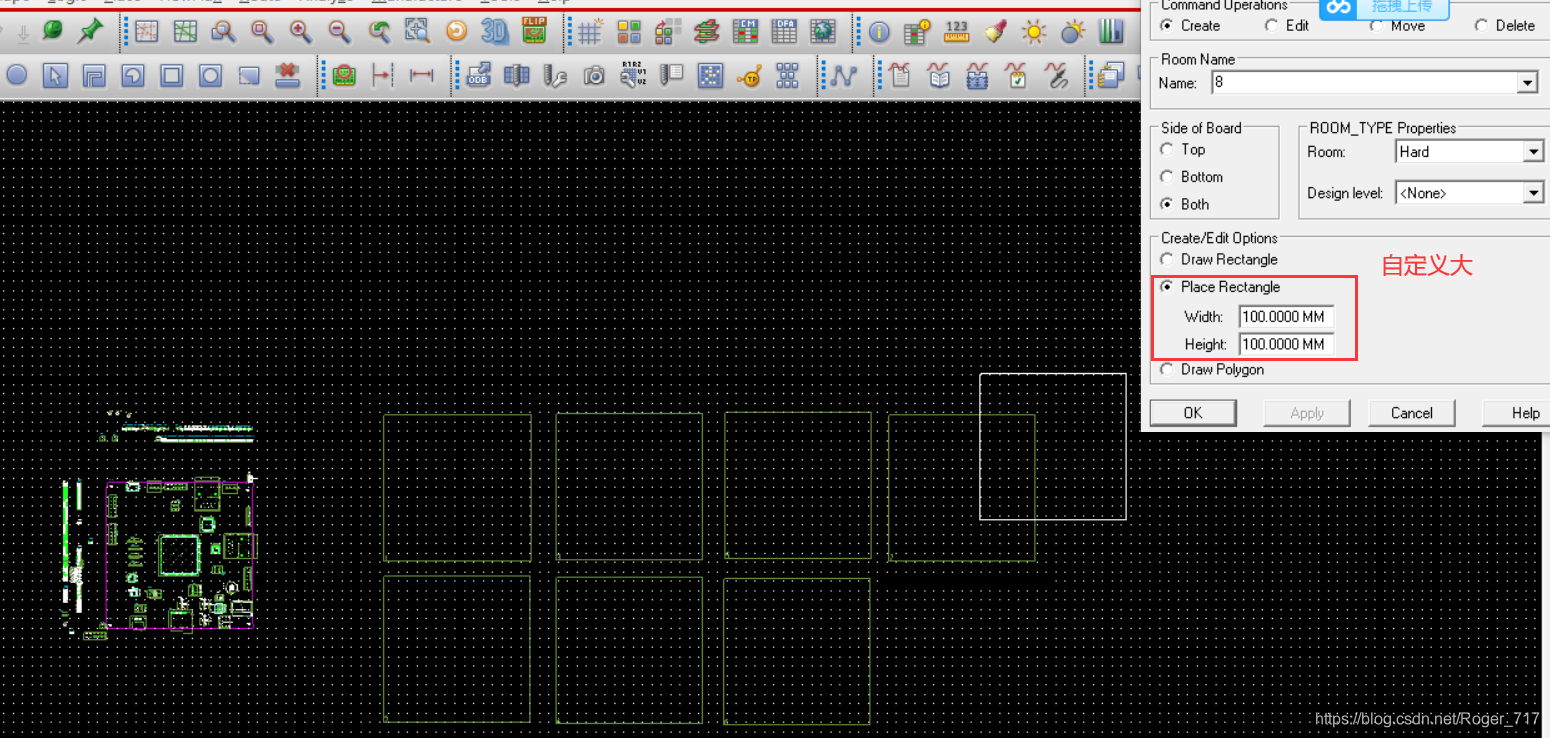

Setup -> OutLine -> Room OutLine

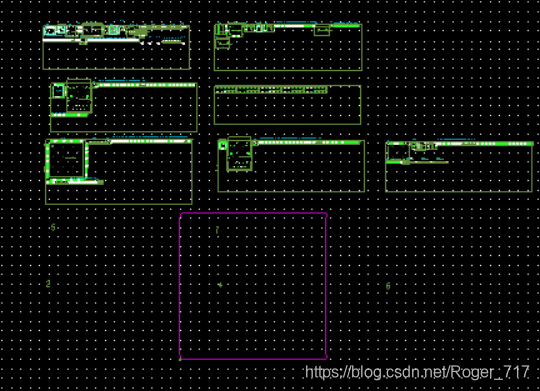

点击之后在绘图空间绘制一个矩形,就会出现一个放置区域,这里是自定义方框大小。

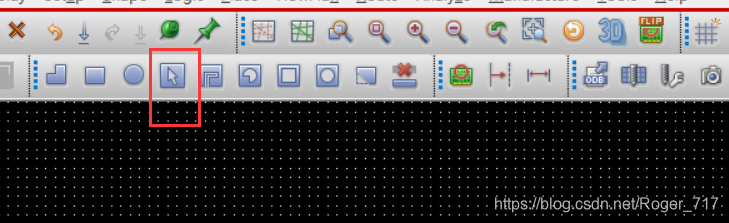

这个可以按键可以将Room边框进行调节。

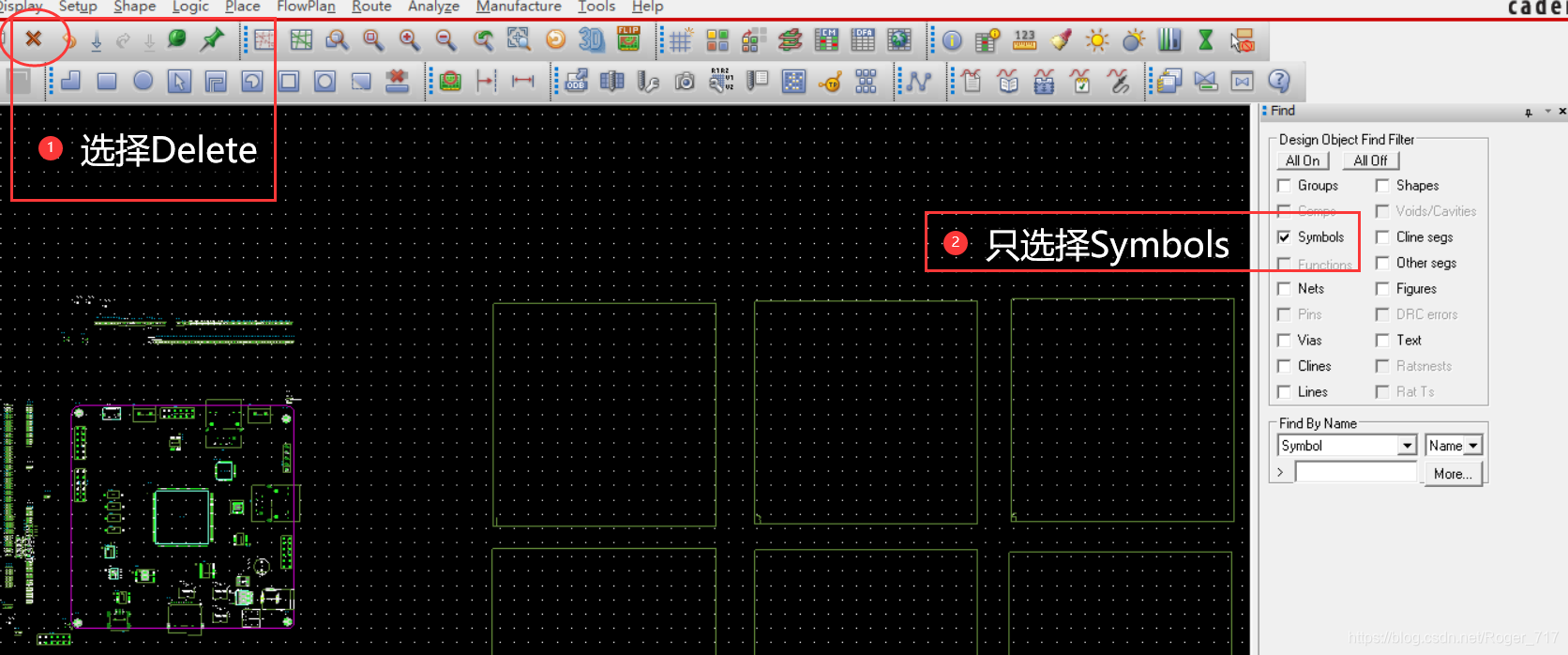

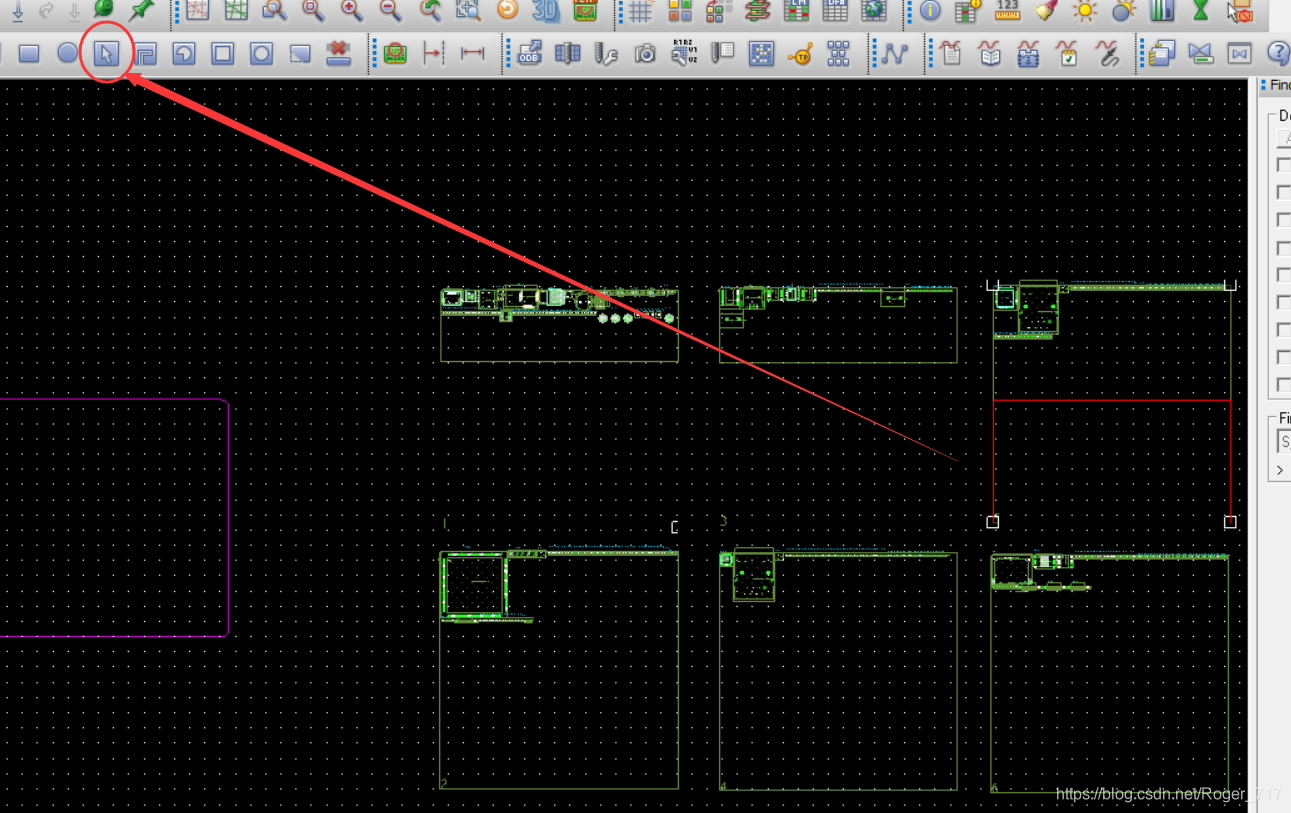

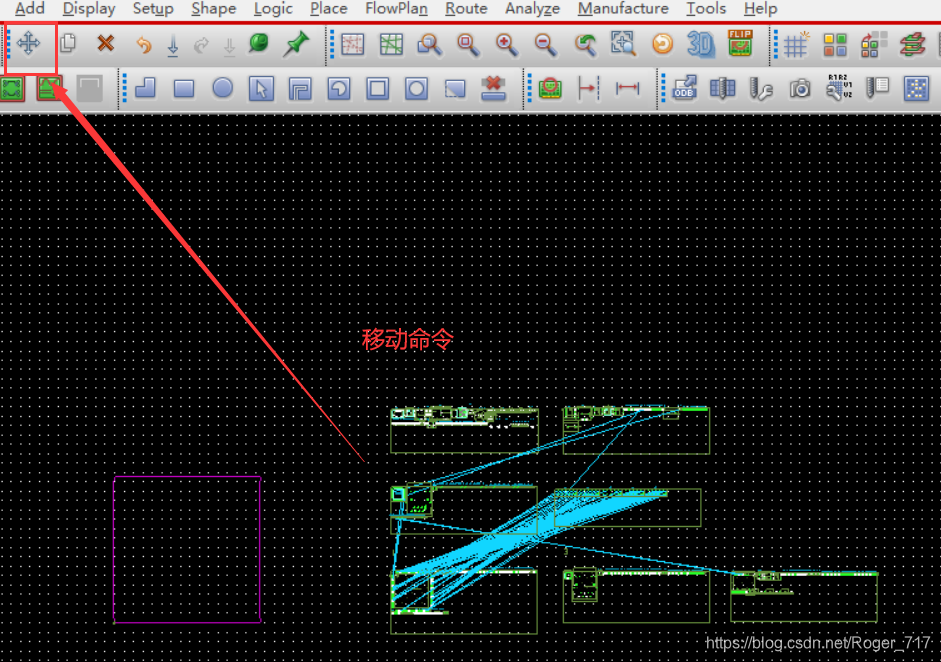

然后框选整体元器件,再单击一下,布置的元器件就会删除掉。重新按照Room放置。

点击Place -> QuicklyPlace

通过这个按钮调节大小。

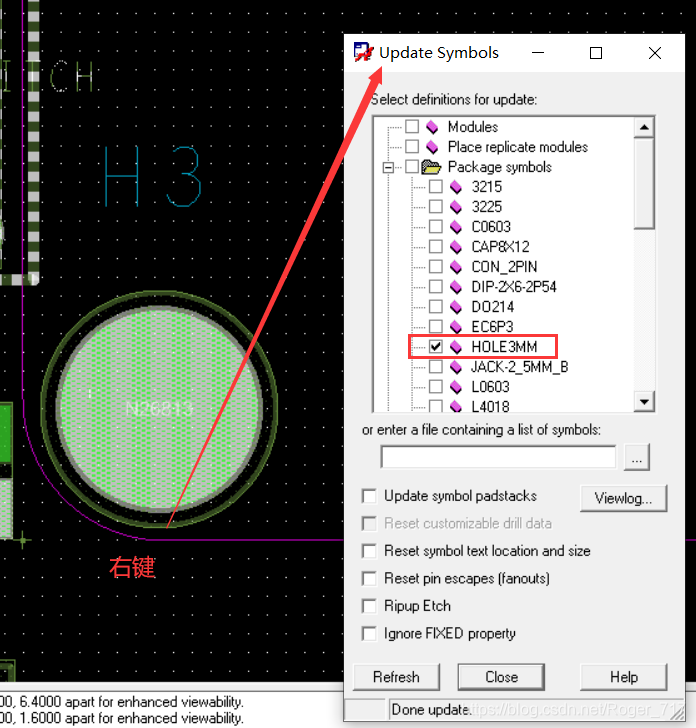

如果画错了封装,对封装进行了更改,如下操作即可更新封装。

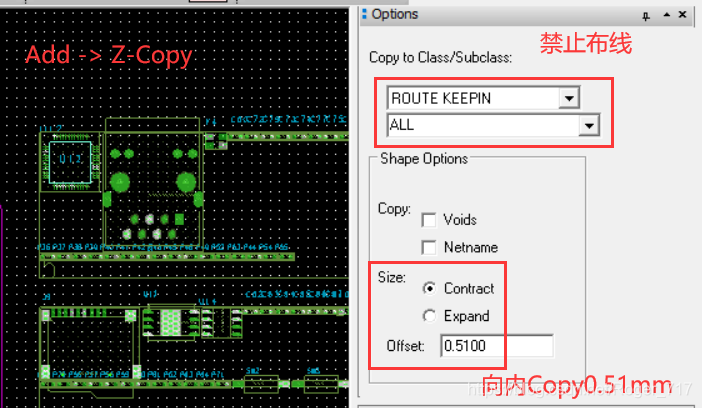

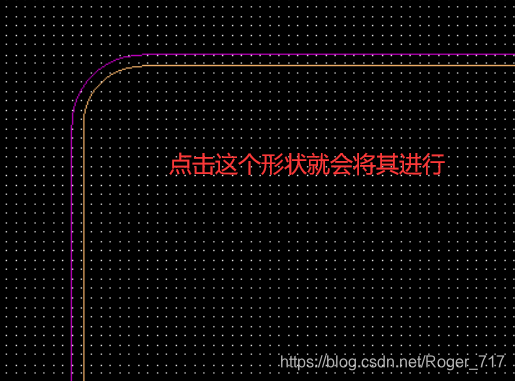

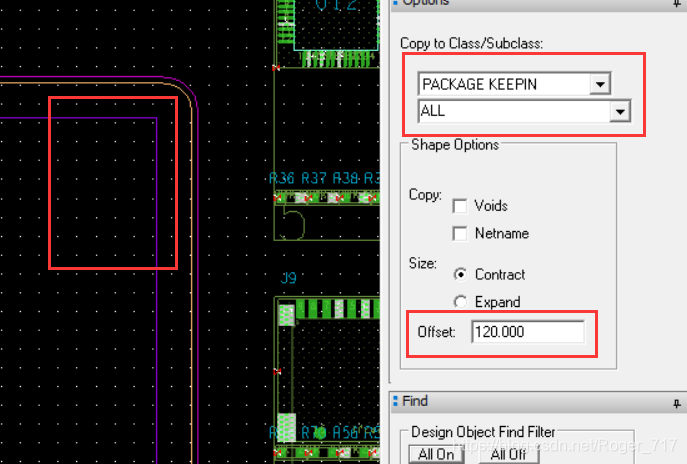

原则上板子边20mil以内不让布线,利用Edit -> Z Copy进行实现。这个命令就是沿着外形向内或者向外Copy一个同样形状的图像。如果这个边框是由线组成的,就需要将线转变成Shape一个完整的封闭图像。

Route Keep Inz禁止布线层。

如果这个形状是线Line,还需要将线 转换 为Space

选择Shape -> Compose Shape

然后选择将要转换的层Outline,框选之后点击Done。转换完成之后就可以了。

同样利用Z-Copy指令

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删