本博文为个人在学习Cadence Virtuoso时的记录,巩固自己学习的同时,也给其他初学者一些参考,学习过程中使用到的软件为Cadence IC617运行在 CentOS7系统 下,参考的书籍为Razavi的《模拟CMOS集成电路设计》。

这是第二篇学习记录,里面记录了对CS放大器的一些分析和仿真。基本的Virtuoso操作就不过多赘述了,在我的上一篇博客中介绍过了,有需要的朋友可以参考:【Cadence Virtuoso】IC学习笔记1:基本操作(以NMOS特性曲线仿真为例)

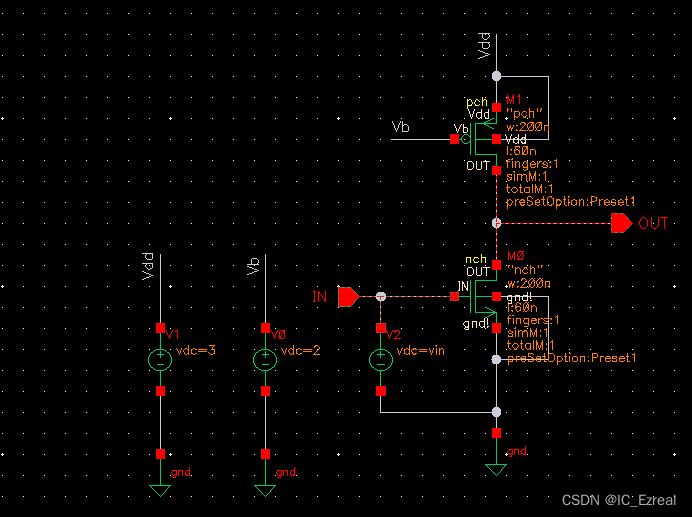

以 电流源 为负载的共源级放大器应用比较广泛,其放大倍数比较高,但是会限制输出电压摆幅,而且如果用PMOS作电流源消除体效应带来的非线性,会增大器件尺寸。 A v = − g m ( r o 1 ∣ ∣ r o 2 ) A_v = -g_m(r_{o1}||r_{o2}) Av=−gm(ro1∣∣ro2).电路原理图如下:

电源电压Vdd设置为3V,PMOS电流源偏置Vb为vb(变量),输入信号 V G S 1 V_{GS1 } VGS1设置为vin(变量)。

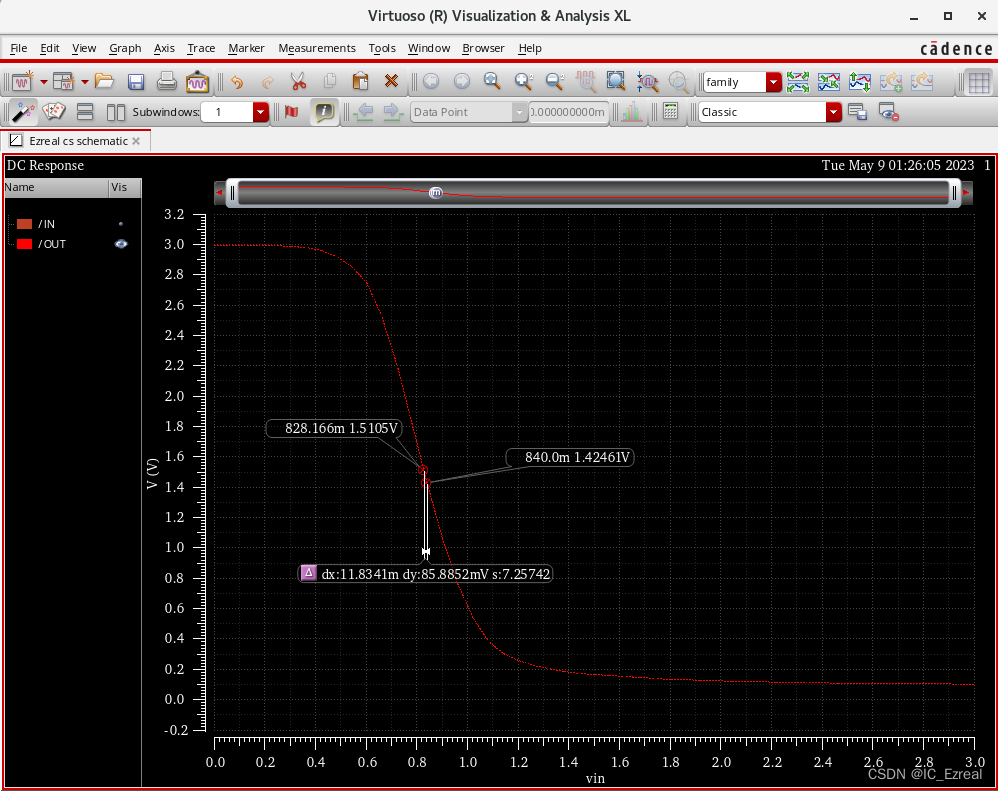

选择dc仿真,将vb初始值设为2V,扫描vin从0V-3V,观察Vout随Vin的变化.结果如下图:在Vout为大概Vdd/2处按快捷键R和D,查看增量,计算增益 A v = − 7.26 A_v=-7.26 Av=−7.26

vb=2V时,PMOS始终导通,当Vin从0V增大到3V,PMOS先进入深线性区,Vout基本为电源电压,然后当Vin大于NMOS的导通电压,NMOS进入饱和区,PMOS也进入饱和区,随着漏电流变大,输出电压开始下降,直到NMOS进入线性区,电压降到最小(几乎为0).

根据曲线可以大致确定静态工作点在 V i n = 800 m V V_{in}=800mV Vin=800mV时,查看管子此时的详细信息

r o 1 = 71.67 K , r o 2 = 57.76 K r_{o1}=71.67K,r_{o2}=57.76K ro1=71.67K,ro2=57.76K

g m 1 = 207 μ A / V g_{m1}=207\mu A/V gm1=207μA/V

A v = − g m 1 ( r o 1 ∣ ∣ r o 2 ) = − 6.62 A_v=-g_{m1} ( r_{o1} ||r_{o2})=-6.62 Av=−gm1(ro1∣∣ro2)=−6.62理论计算结果和实际差不多。

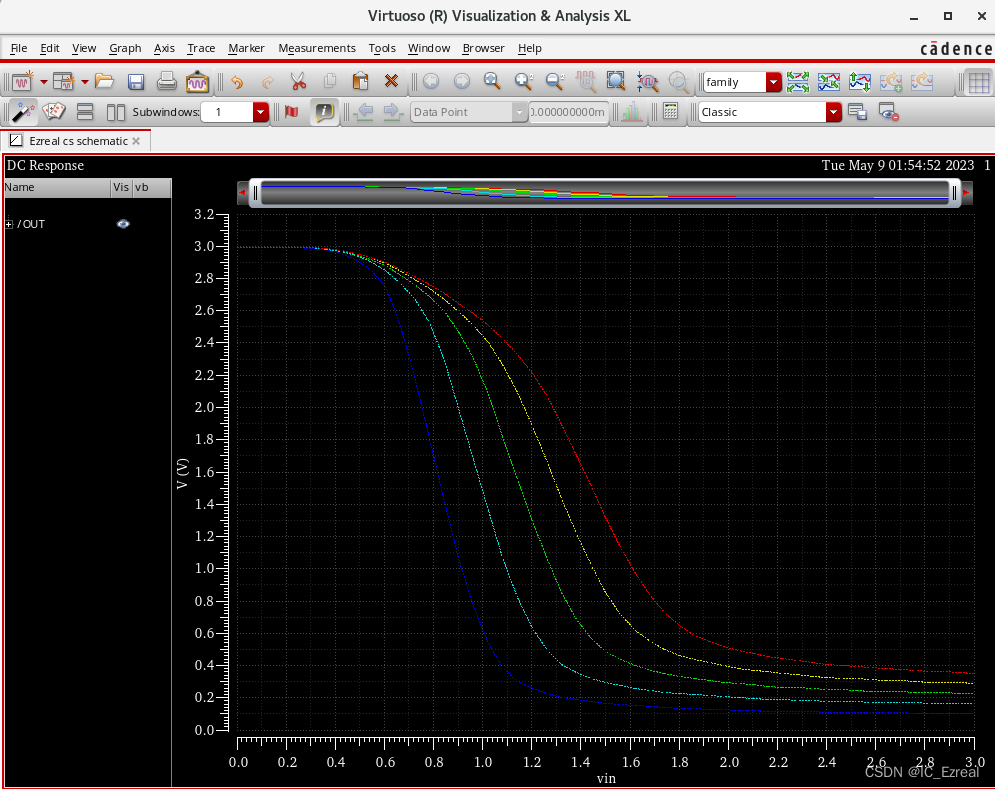

将vb作为参数扫描,从1V-2V仿真5个点,结果如下:

随着Vb的减小,增益变小了,这是因为,电流源的电流变大,饱和区中管子的 g m g_m gm虽然变大,但由于沟道调制效应, r o r_o ro急剧减小,导致增益最终减小。

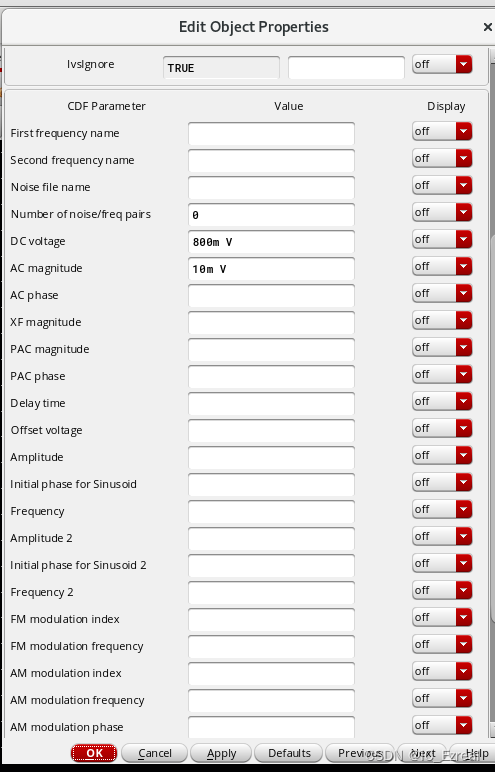

为了获得最大的增益,将直流工作点设为800mV,因为已知增益大概是6~7之间,为了摆幅明显一点,将交流输入幅值设为100mV。

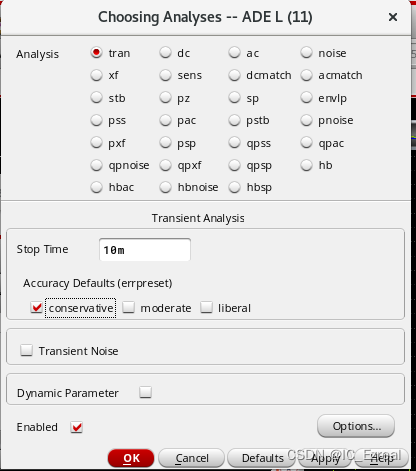

选择第一项“tran”,仿真时间根据设置的频率来,这里设置10ms,仿真 精度 选择最大仿真精度,然后ok。

注意:瞬态仿真的时候要设置电源,vsin中Amplitude是输入的幅值,Frequency是频率,1KHz。

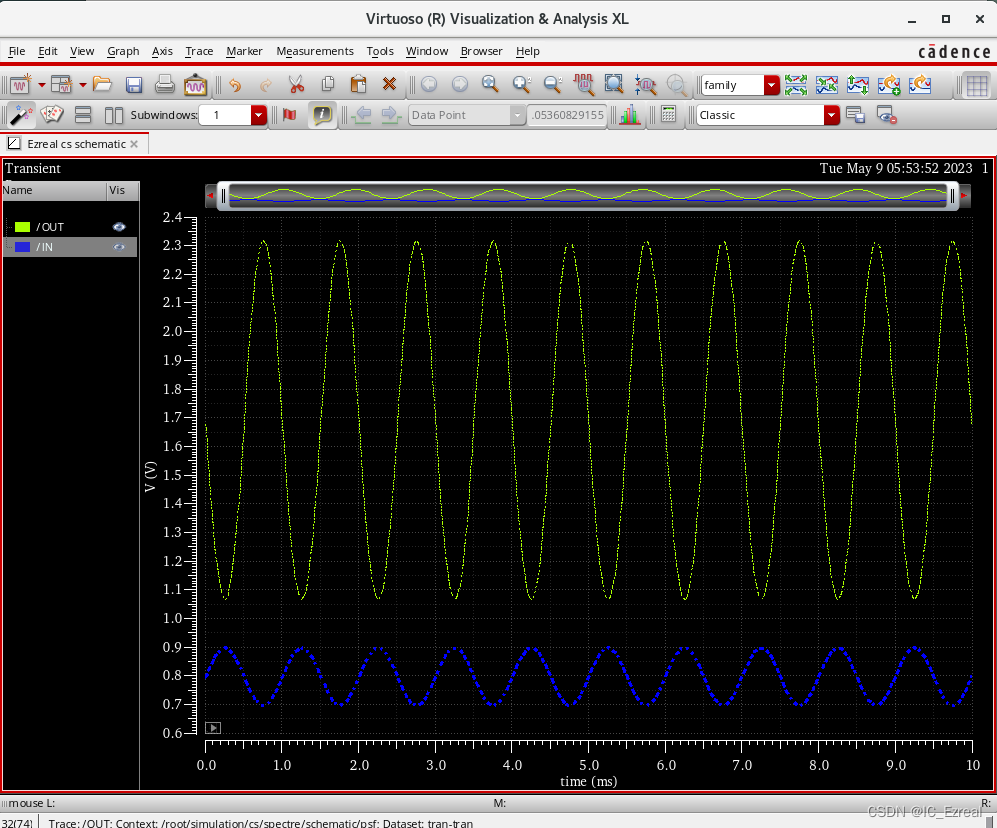

结果如下图所示,交流信号被放大了理论计算的倍数。

注意:vsin中设置AC magnitude 是幅值,不用设置频率,要把前面瞬态仿真电源的设置删了。

仿真设置中选择ac,扫描频率,从10KHz到1000Mhz。(后来发现100M的时候还没到第一个极点)

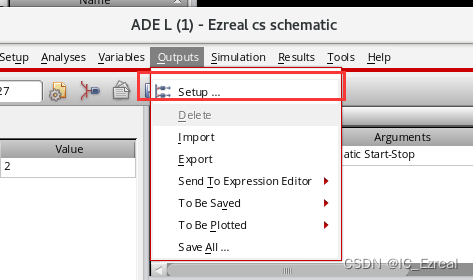

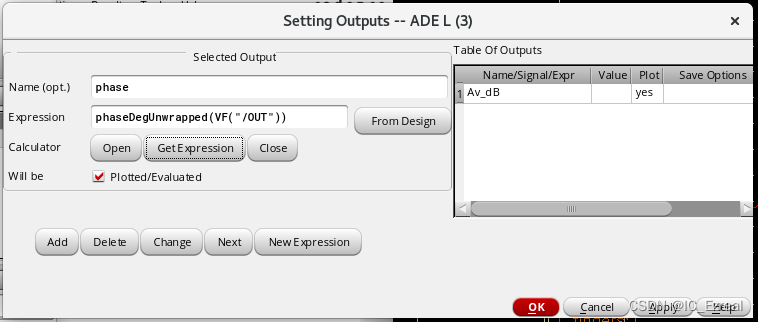

输出我们想得到幅频和相频特性曲线,选择Outputs->Setup.

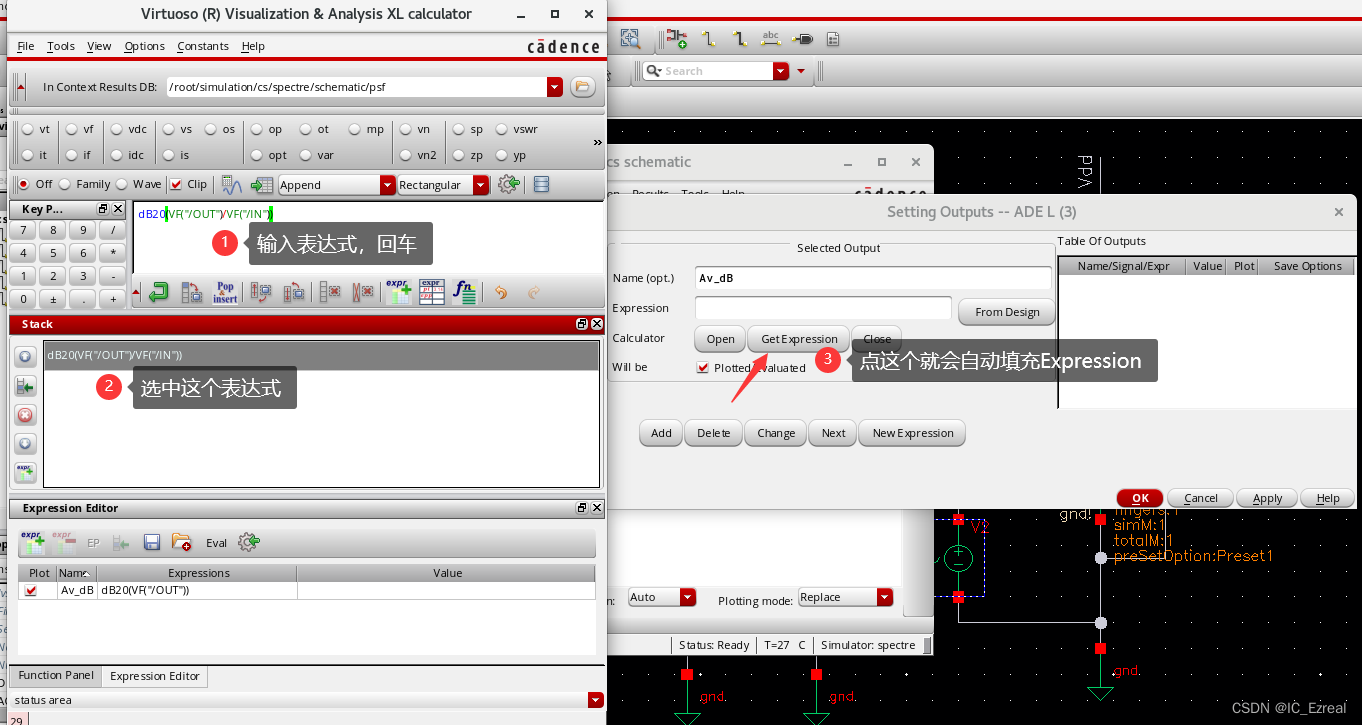

然后输出一个表达式,给这个输出命名为Av_dB,然后点击 Calculator 中的OPEN,打开公式编辑器。 表达式为dB20(VF(“/OUT”)/VF(“/IN”)),注意这个OUT和IN跟你的信号label名称有关,不是固定的。

表达式为dB20(VF(“/OUT”)/VF(“/IN”)),注意这个OUT和IN跟你的信号label名称有关,不是固定的。

相位表达式的添加同理,phaseDegUnwrapped(VF(“/OUT”))。

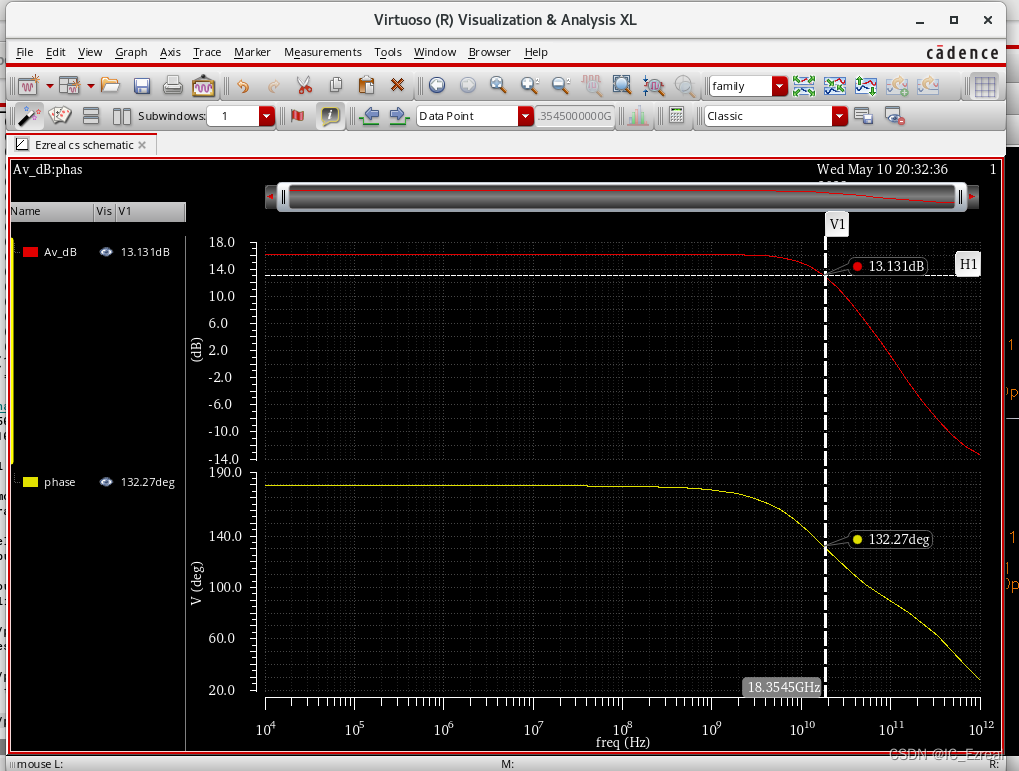

然后开始仿真,结果如下,点击右上那个图标可以把曲线分开看:

根据第六章频率响应学过的知识,增益减小3dB的点的频率就是第一个极点,相位会减少45°,可以添加marker验证一下。

至此,交直流瞬态仿真以及基本看一些参数都完成了,接下来要开启大作业了——二级放大器的设计,不得不吐槽一下,我们老师才讲到Razavi的第七章,就让设计二级放大器,我看了一下题目要求,发现很多名词都没见过,还得自学,二级放大器涉及的基础知识貌似得学到第十章,加油!

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删