软件

产品

统一的系统级IC和封装设计平台。

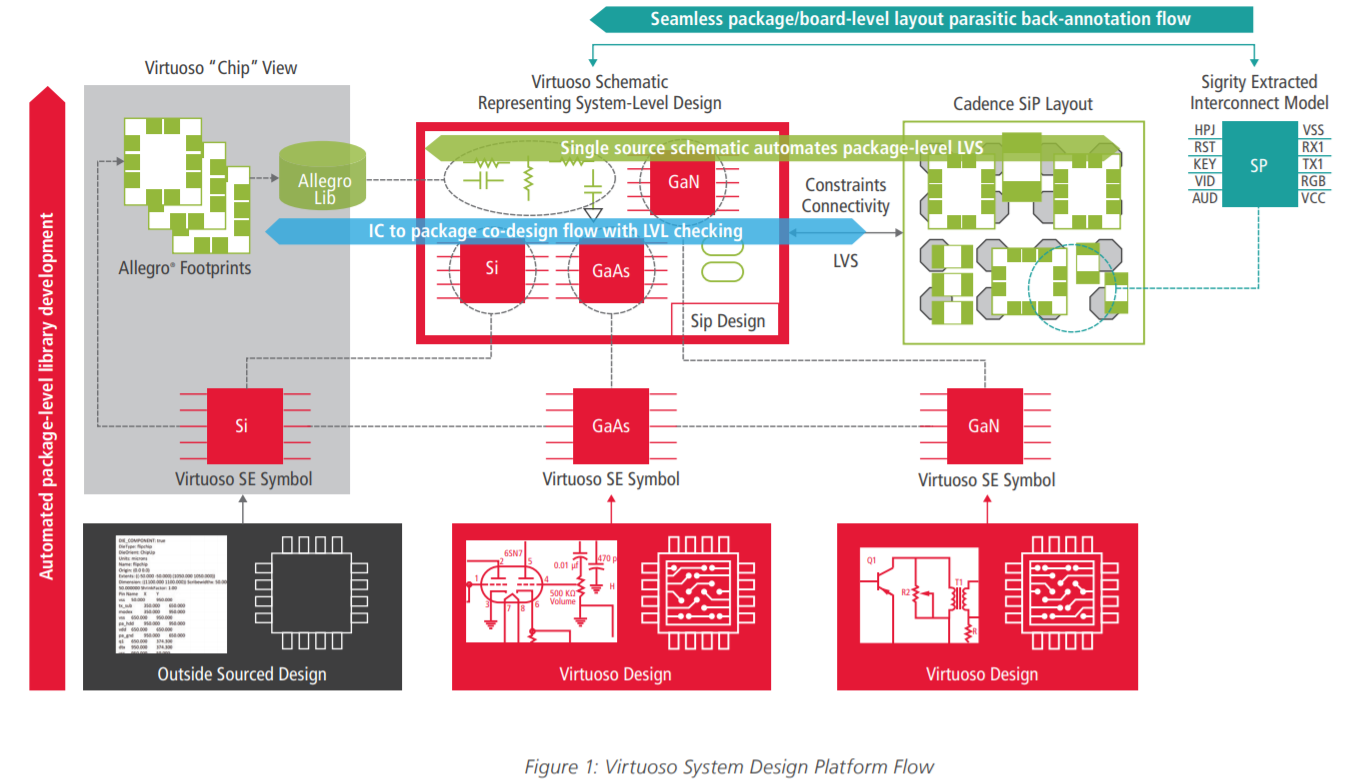

Cadence® Virtuoso® 系统设计 平台是一个基于系统的整体解决方案,提供了从单个原理图驱动IC和封装的仿真以及LVS(Layout Versus Schematic,布局与原理图验证)干净布局的功能。 有两个关键流程:实现和分析。

实现的工作流是使用Virtuoso Schematic Editor创建IC封装原理图,然后将原理图转移到Cadence SiP Layout进行物理布局,除此之外,还可以生成和验证库单元,输出BOM(bill of materials,材料清单),进行LVS验证(Layout Versus Schematic checking,布局与原理图验证)。

分析的工作流是提取和仿真系统(IC-封装-PCB)任何布局状态下的任何部分。而且还可以为PCB和IC封装布局自动生成原理图,为IC模型或原理图绑定封装,使用Virtuoso ADE Product Suite和Spectre® Multi-Mode Simulation接口构建测试文件(testbenches)对系统进行仿真。从PCB和IC封装布局中提取的Cadence Sigrity™模型会自动匹配到生成的原理图中。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删