1.virtuoso无法启动Cadence61 所对应的virtuoso程序

可能是因为管理员安装的时候并不是用的virtuoso这个名字,需要你在/usr/local/bin/目录下查看你的cadence程序是什么名字,比如我其实管理员安装的cadence61的程序是 ic617

2.WARNING Ruler layer ‘hilite drawing4’ is missing.启动ic617后发现没法显示,都是一坨黑,还报这个warning,但是发现管理员装了好几个ic617一个大写的IC617一个小写的ic617(真的服了),遂尝试用大写的IC617启动,果不其然,有东西了,看来还是版本问题。

3.在设计和学习ADC时,应该都会用到清华李福乐老师的ppt和相关的例子,我为了能打开它那个例子可谓是费劲心思,绞尽脑汁。

-困难1:

老师给的压缩包里只有tsmc18scx(TSMC 0.18um 数字标准单元library),里面只包含一些数电中的门,那mos管对应的库去哪找呢(因为直接启动设计library会报找不到tsmc18库中的nmos pmos这样的错)。所以得出结论我得找个tsmc18的库。我去网上找啊,找啊都没找到,终于问学长,学长说服务器上有,可把我高兴坏了,赶紧找到拷过来。

-困难2:

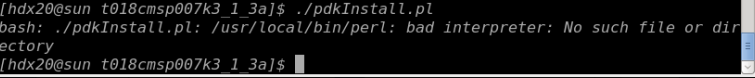

tsmc18是拷过来了,我以为简单的解压一下那几个文件就可以了,于是添加到cadence的library path里面,哦豁,果然没那么简单。我去网上找,又看了看安装说明文件(README.INSTALL),知道得用pdkInstall.pl进行安装,好吧那就运行吧,但运行完它报错(bad interpreter…),我一看完蛋我不会要按照它说的第二种方法手动安装吧。然后又去问学长,“我们的服务器上会不会没装perl啊”,学长直接perl -v,好家伙,装了perl的,然后学长说可能是这个程序没有找到perl在哪,我心想有道理啊,于是我就开始翻找perl(资深windows用户哈,对linux的命令极其不熟悉,不要嘲笑),然后在我找到perl的同时,学长说我登上服务器给你改了一下pdkInstall.pl第一行里perl的路径(用which perl可以找到perl的路径),白翻半天了,不过这个问题算是解决了。然后便进入pl文件的运行安装过程

-困难3:

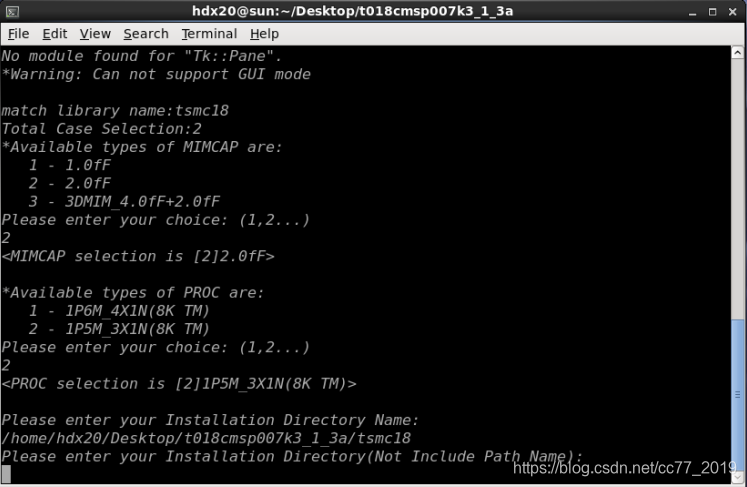

安装的过程中本该一路顺利(安装选项我随便选的,因为我只是想打开李福乐老师的例子看看而已,哪个工艺库并不重要),结果给我卡在选安装路径这里。不管我输什么路径,它都让我重新输,并且打个括号说(Not Include Path Name)不明白啊,咋办嘞,就卡在这里了。然后后来无意间我啥也没输然后回车,居然进入了下一步,我再选择y(表示确认),它报错说无法创建,突然醒悟,**它的意思是一个文件夹的名字而不是路径!**看来还是英语理解的不够,Directory Name 和Path Name是两个东西哈。于是我就随便输了个名字pdk,然后便顺利的完成安装了。

-困难4:

你以为安装完导入进去就结束了吗,我也曾经以为。我发现我在服务器找的这个tsmc18的库是oa格式的就是说是cadence61之后支持的格式,而老师给的设计库 SAR_ADC_8BIT_V1 以及数字标准单元库tsmc18scx都是cadence51的格式,你说cadence也是离谱,更新就更新嘛,为什么对低版本不兼容??cadence只提供了cdb转oa的转换工具哈,于是便需要把这两个库转成oa格式,具体操作可以参照这个博客cadence51的cdb格式转cadence61的oa格式的方法

好了历经这4大磨难我终于能打开李福乐老师的那个例子了。

另外知乎上有一篇导入李福乐老师的SAR ADC并进行仿真的教程,b站上也有对应的链接,但是它给的库并不全,同时那个库也比较老了好像是0.5um的tsmc的库,本文用到的工艺库和设计库都是老师给的,不知道允不允许发到网上,所以不敢发,包含这些文件:

SAR_ADC_8BIT_V1.tar.gz:一个基本的8bit SAR ADC电路library;

tsmc18scx.tar.gz:TSMC 0.18um 数字标准单元library;

t018cmsp007k3_1_3a:内含tsmc0.18um的工艺库。

4.利用UMC28nm的库进行3bitSAR ADC的设计

-困难1:

由于ADC其实是一种数模混合电路,里面需要用到一部分的数字标准单元也就是Standard Cell Library,你有两个方法来获取它

一个是你自己画,把那些与门与非门或门都画出来,但是工程量较大,适合对相关工艺有一定积累的公司,一般来说要把数字的门用到模拟的设计里面更可靠的方法是这个,但是对于学生来说工作量太大。

一个是一些公司会做对应工艺下的Standard Cell Library用于数字设计,ARM和Synopsys都会有做,有一些下载途径但具体怎么下载我并不知道。

我采用的是第二种方法,问了好些人总算是要到了ARM公司的在UMC28nm下的Standard Cell Library。那么问题来了我要如何把它给的这些文件导入到cadence virtuoso里面呢?我在网上找啊找,终于找到了一篇说得还算详细的吧,但也没有很详细。所以后面又请教了一些工程师才完成这个过程。(得到一个血一样的教训,还是应该等研究生上完课再开始做设计啊!!工程师说这些研究生会有课程讲,奈何我是个本科生呢)

下面是导入数字标准单元库到cadence virtuoso617的总结。

首先,先在library manager处建立一个库,并且和.tf文件完成绑定。

建议先导入symbol!!

然后,到cadence的主窗口就是启动页面

点击 file -import

导入schematic:

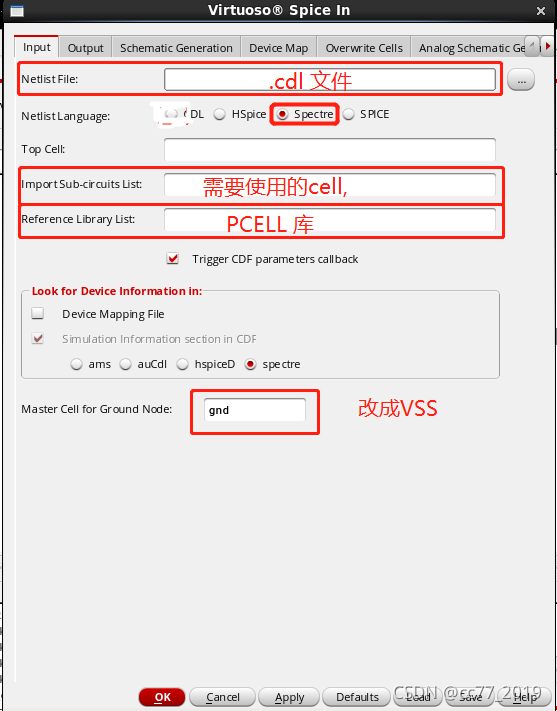

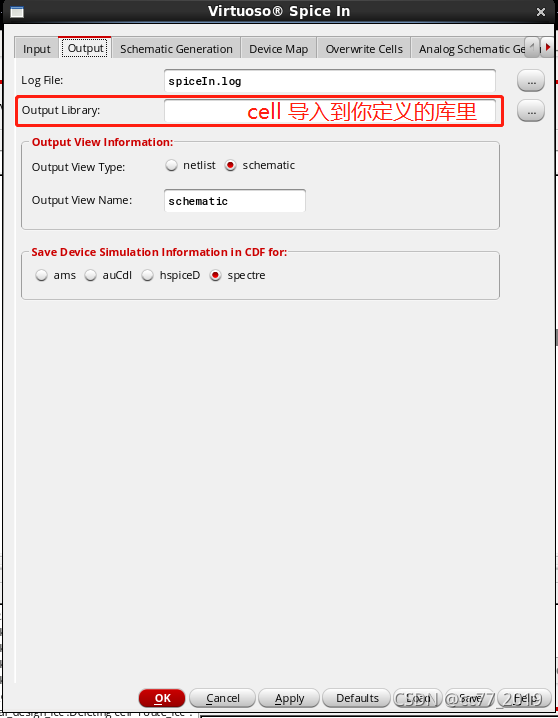

在import中选择Spice,然后在ARM给你的那个Standard Cell Library的文件夹里面找到.cdl文件,进行如下配置:

首先是input

如果所有cell都要导入 Import Sub-circuits list可以不填

(reference library list我也不知道写啥,我随便写了一个我这个Standard Cell Library对应的工艺文件UMC28hpc的工艺库)

然后是output:

我只导入过ARM的Standard Cell Library所以对于其他库,如果设置可能有所变化,可以自己试试,我刚开始以为cdl文件要用cdl的Netlist Language,但是后来发现要用Spectre才行。

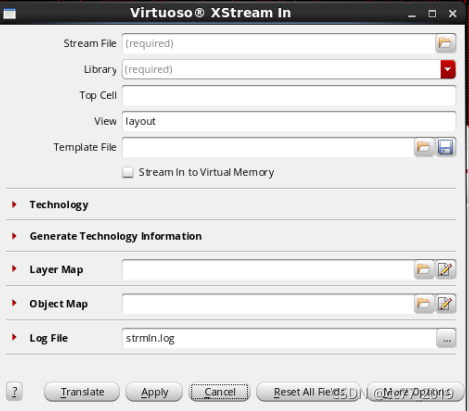

导入layout:

在import中选择Stream,就填前两项应该就行,Stream File是.gds文件或者.gds2,可以找找。

导入symbol:

对于symbol文件一般会有,直接传到服务器上即可,因为本来应该使用.v文件,import的时候选择verilog去导入的,但是那样出来所有的门都是长方形就不太好看,一般ARM或者Synopsys公司给的包里会包含symbol的库。直接用sftp传到服务器上就好了。

5.安装smic55nmpdk文件,报错Error: Cannot find virtuoso executable. Please reset PATH or specify it by argument “-b <virtuoso_bin>”

可能因为该目录下没有配置相应的cadence virtuoso的环境,先输入ic617-env之后再安装pdk即可。

6.启动cadence virtuoso,报错 WARNING file /home/hdx20/CDS.log fflush failed. No space left on device。

清理一下磁盘中的东西,应该是分配给用户的空间被占满了,导致无法启动。

7.修改了原理图的pin,如何更新symbol中的管脚,而不重新排。

从schematic再次create,系统会检测到已有symbol,直接选择modify即可。

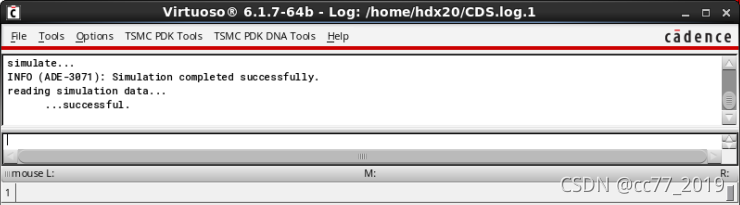

8.仿真时报erro:“xxxxxx”(之后再具体截图原因)

主要遇到过以下几种:

a)没有setup 合适的library,有的时候工具不会自动给你检测并添加,也就需要自己找到.scs文件导入一下。(操作:set up-model libraries)

b)找不到spectre,因为我导入的是学长的设计,所以仿真时会报错这个,可以把对应view的spectre文件删了,不影响原理图仿真。

simic40ll工艺

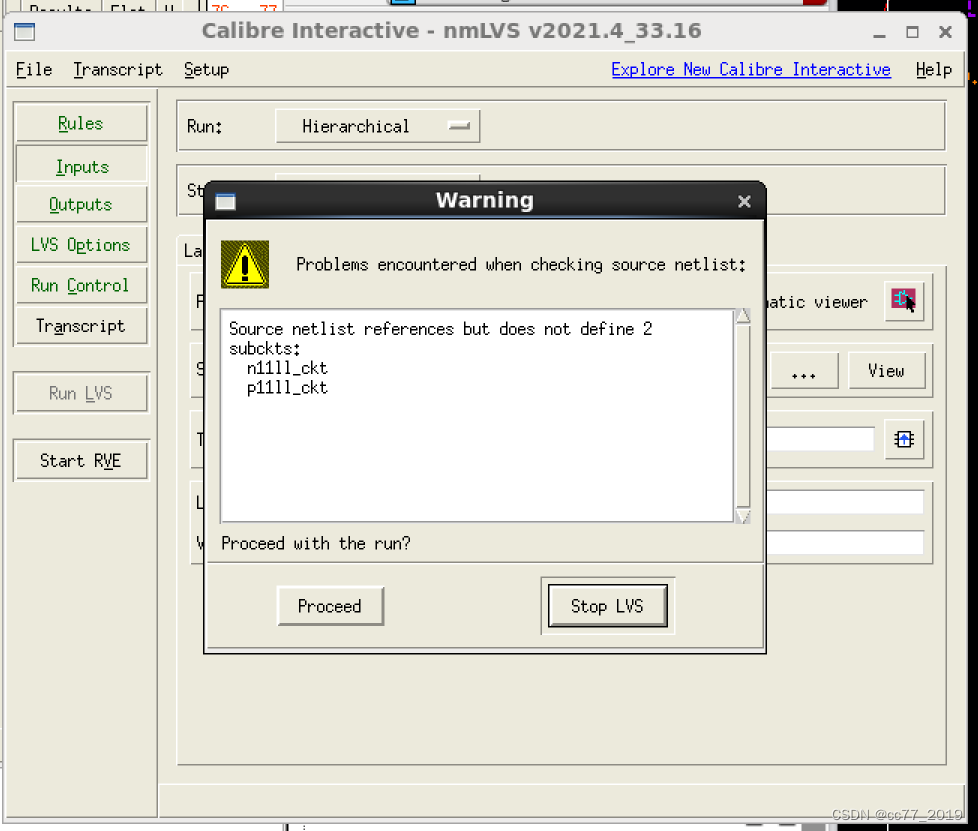

1、lvs时报错:Problems encountered when checking source netlisttSource netlist references but does not define 2subcktst n11ll_ckt p111l_ckt

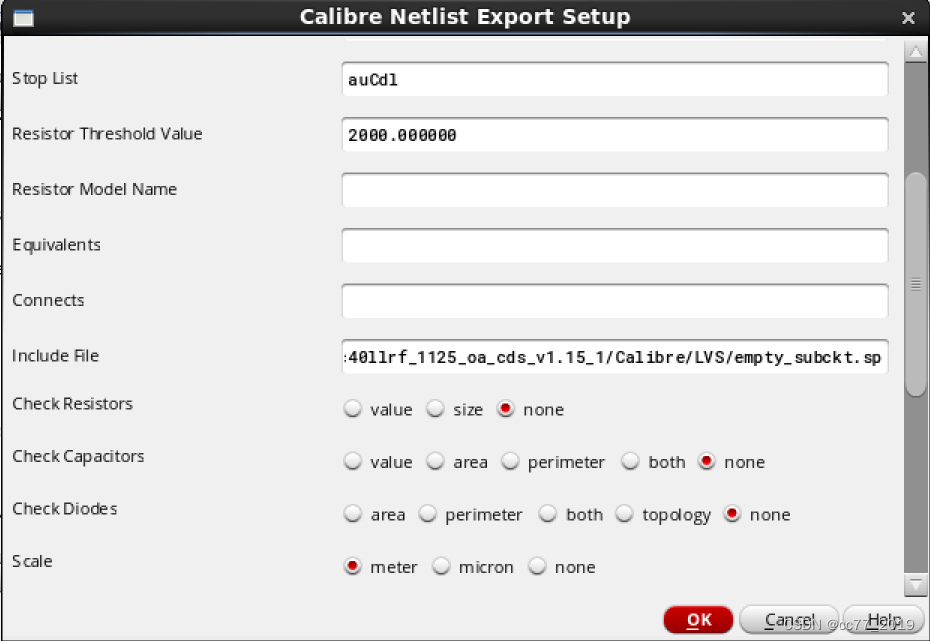

需要在calibre-setup-netlist export,把.sp文件include进来,因为你从原理图通过calibre生成的网表文件,你的n11ll_ckt这些mos的名字,和你的lvs规则文件里用的mos的名字不是一个,因为simic的lvs规则文件对网表里mos的文件有一个简化映射。

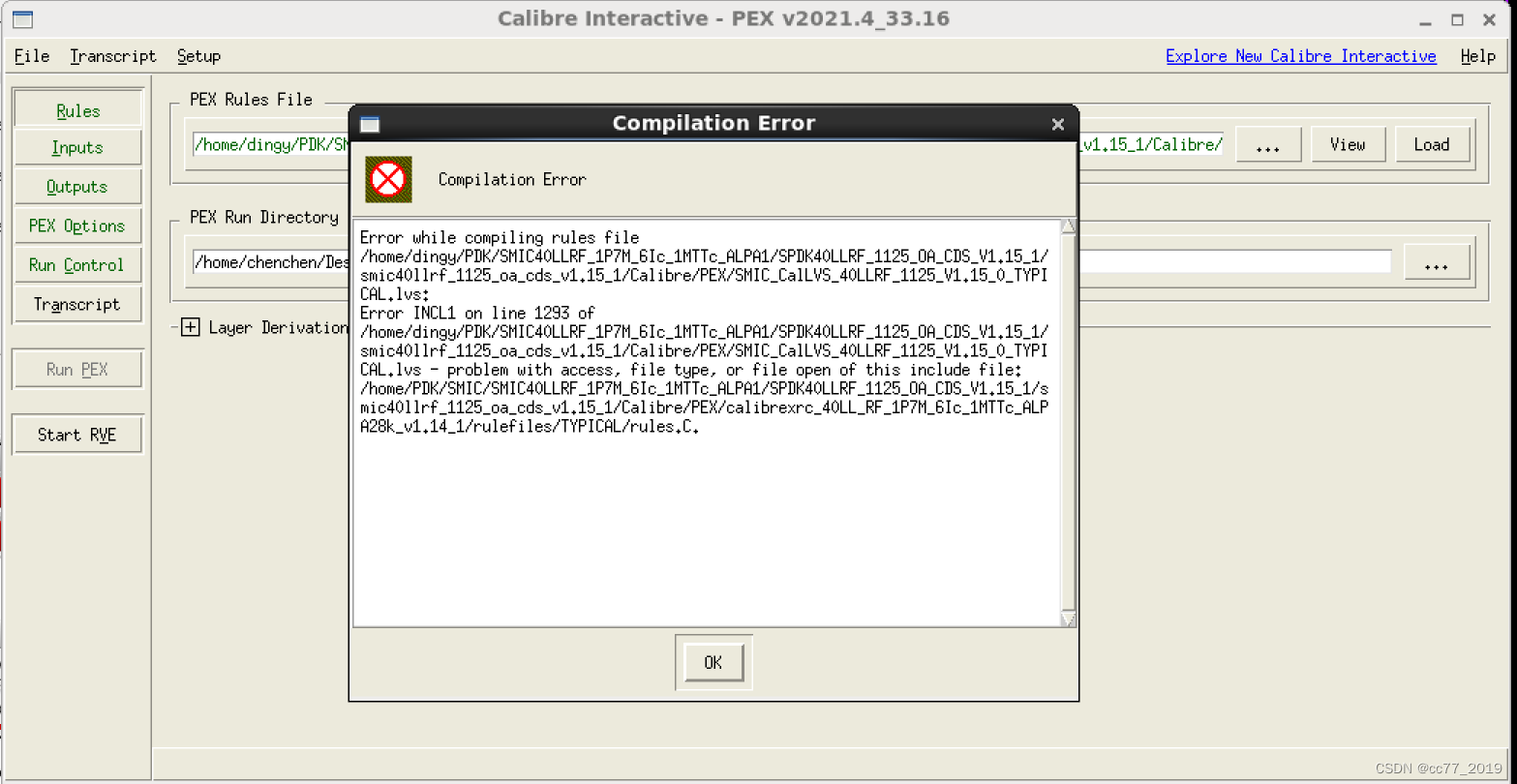

2、pex报错,Compilation Error :Error while compiling rules file。(特别神经的是它的pex rules文件居然是.lvs后缀的,simic一般会在里面留一个typical_pex的一个文档说明各个文件是代表什么的,我找了好半天)

仔细查看报错,可以发现这个是rule文件include的是绝对路径的文件,由于路径不符合目前的路径,所以你需要找到.lvs的文件报错的那行并且修改为你的服务器对应pdk的绝对路径。

3、SMIC40nm,跑MonteCarlo时,只需要添加相应的mc corner(mos_mc res_mc mom_mc),保证schematic中的mos下的mismod置1了(q一下mos在properties里面就可以看到,默认是打开的)。

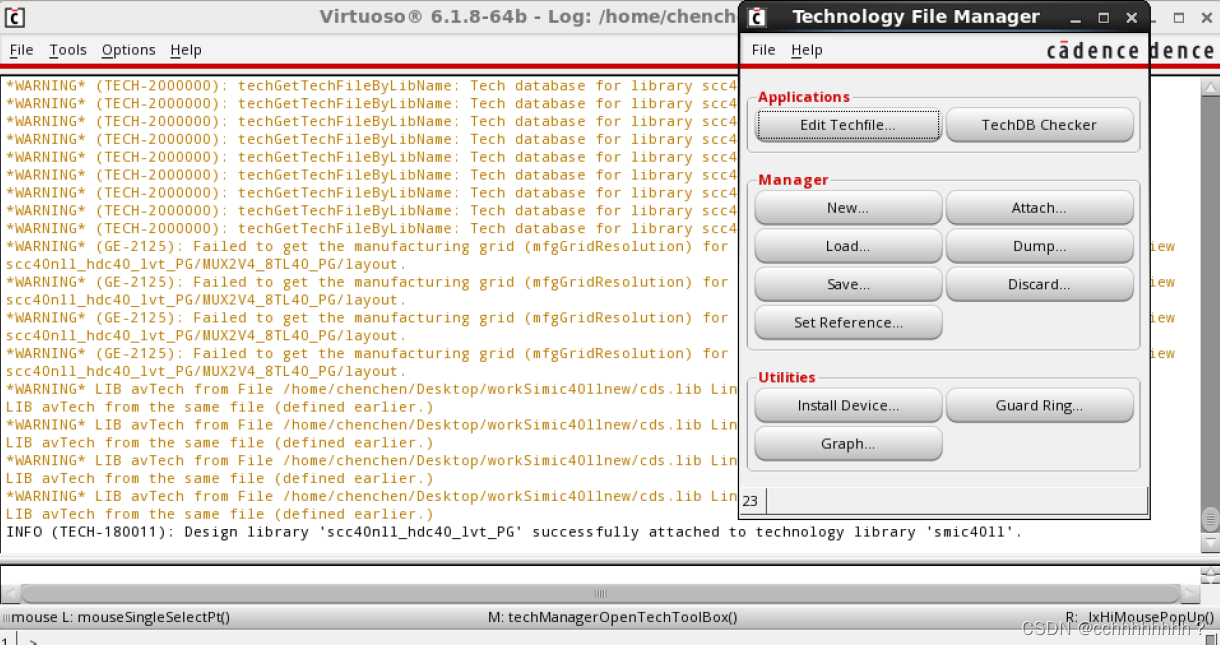

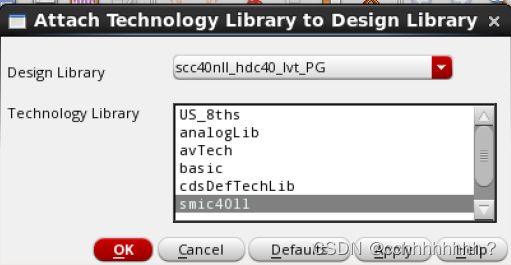

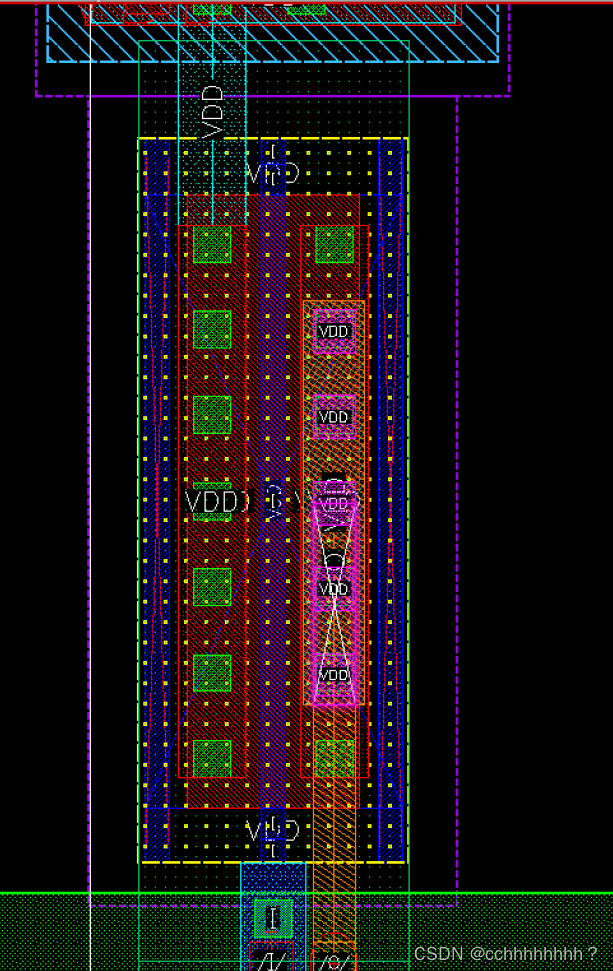

4、scc40nll_hdc40_lvt_PG库中 layout 打开一片黑

需要重新bind一下Technology lib:

virtouso窗口-tools-technology file manager-attach-绑定到simic40ll

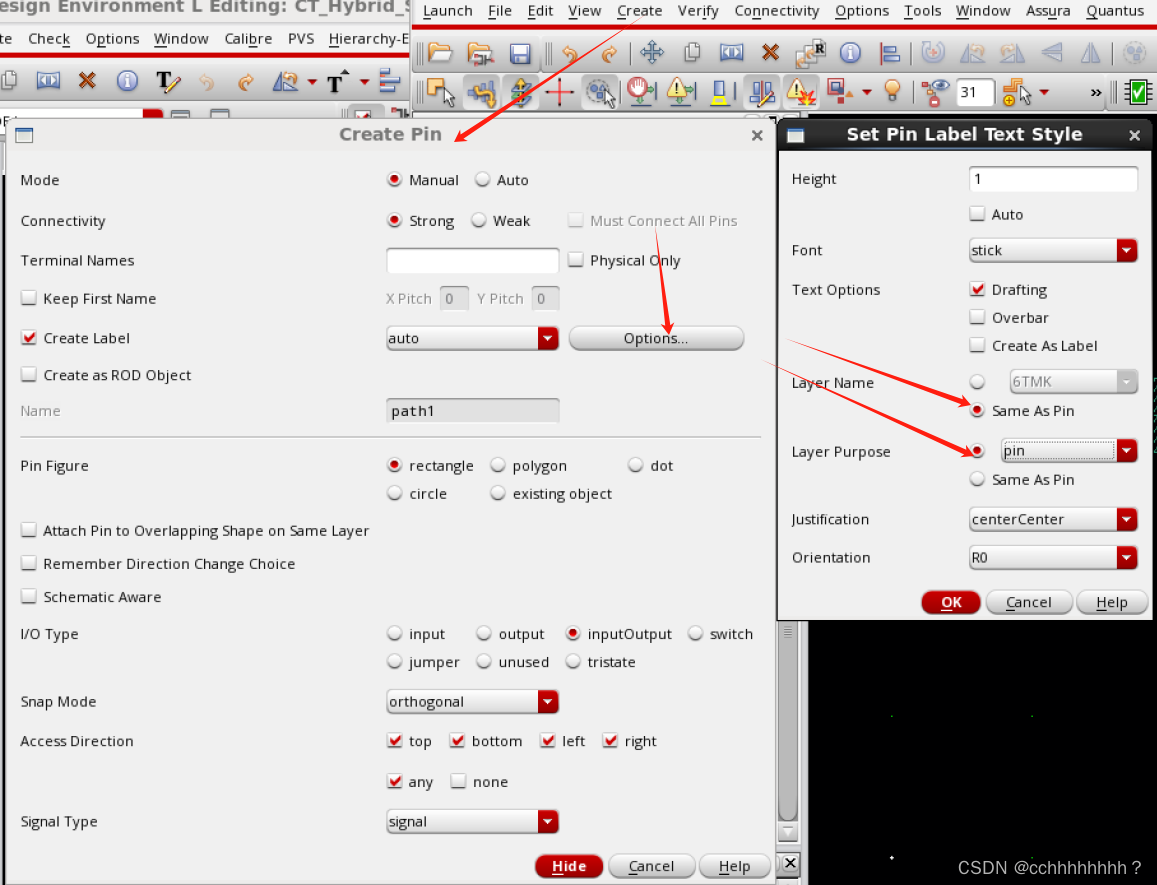

5、pin不带label

create-pin-create label √-options-layer name same as pin-layer purpose pin

6、smic40的工艺,dnw需要res层,不打res层可能会识别不到管子,和net,也可能把错误报到net上面去。

7、把mos管打散之后,版图上报warning:Overlap between a pathSeg on ‘M3 drawing’ on net ‘O’ and a rectangle on ‘M2 drawing’ on net ‘VDD’ creates a short.。这是因为打散后layout xl 把net识别错了,q一下有源区的金属图形,改成你想要的net名字就行。

8、Net DVSS is selected for stamping. Rejected nets: AVSS

AVSS DVSS通过NWELL或者PSUB形成了非金属直连上的“软连接”,就是共用了同一个sub。要么通过DNW隔离一下,要么用假的SUBD分开骗一下工具,但是实际制造的时候会是同一个衬底,建议采用DNW进行隔离。

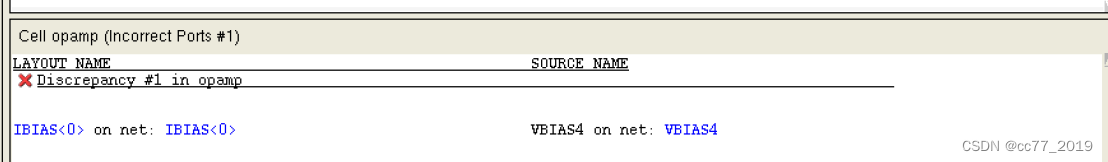

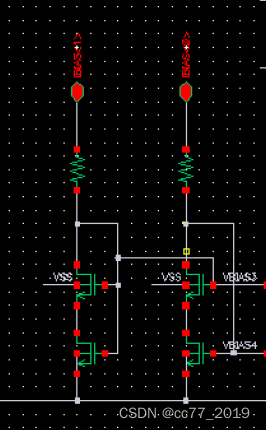

1.IBIAS<0> on net;IBIAS<0> VBIAS4 on net;VBIA54

两个名字不同的net接在一起,lvs就会报这个错。在漏端接一个小电阻即可解决。

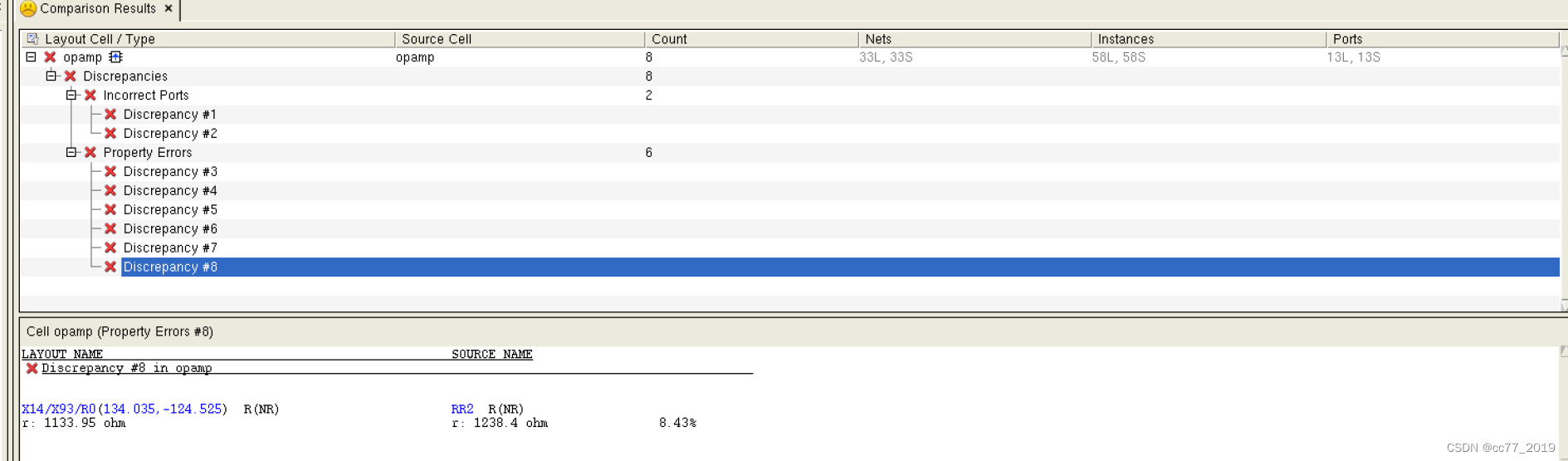

2.电阻阻值discrepancy

我这里本来用的TSMC185V,但是做lvs的时候用的TSMC18的lvs文件,而185V和18并不完全相同和兼容,由此出现了此问题。改用TSMC185V的lvs文件便解决了。

3.后仿看内部节点电压

在原理图里打pin,layout也相应打pin,就可以看了(用于看的节点电压不太多的情况);

如果要看的比较多,就要从result browser里去找才行,反正直接用plot是plot不出来的。

4.后仿真利用spectreText,仿真报错:Attempt to override value of inherited parameter `r’ when instantiating a subcircuit.

ADEL中不要用r,做为变量

养成一个不要用太简单的名词做变量的习惯

1.后仿真增益掉得很厉害,或者相位裕度突然特别差,特别离谱的问题

首先把电源和地的寄生exclude提取网表再重新仿一下,可能因为电源和地走线的问题,导致了额外的环路出现。

2.spectrText反提文件和netlist的调用端口顺序可能不匹配要注意。可能是cadence卡bug了,重启一下。

3.result browser在adexl里面没有节点电压的信息,可能是adexl的bug,点进test editor再用adel仿真一次,后面adexl就能看见result browser的结果。

1.仿真一直卡在xmelab,不往后进行。

解决:AMS卡bug了,换个服务器。

2.ADEL 或者ADEXL仿真一直显示之前的结果,并不更新结果,例如我后一次只仿到40ns,但是却显示到180ns。

解决:ADEL出问题了,用ADE Explorer(官方建议就是用ADE Explorer进行AMS数模混仿)

1、vbit

rptsart(the starting bit when repeating)起始时,vbit输出的是1还是0;

rpttimes(repeat times)vbit输出是根据你的输入的data进行重复的,这个属性指定了vbit重复的次数;

number of periodic jitter:描述了时间周期的变化,当该值不是0的时候,时间周期的变化可以是一种正弦的、三角波的、方波类型的变换。如果只考虑随机抖动的话,number of periodic jitter可以设置为0。

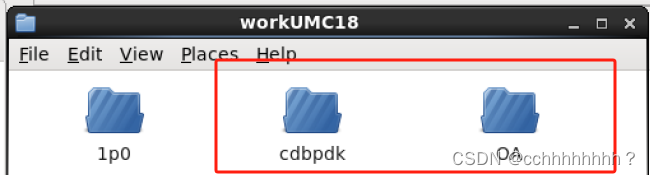

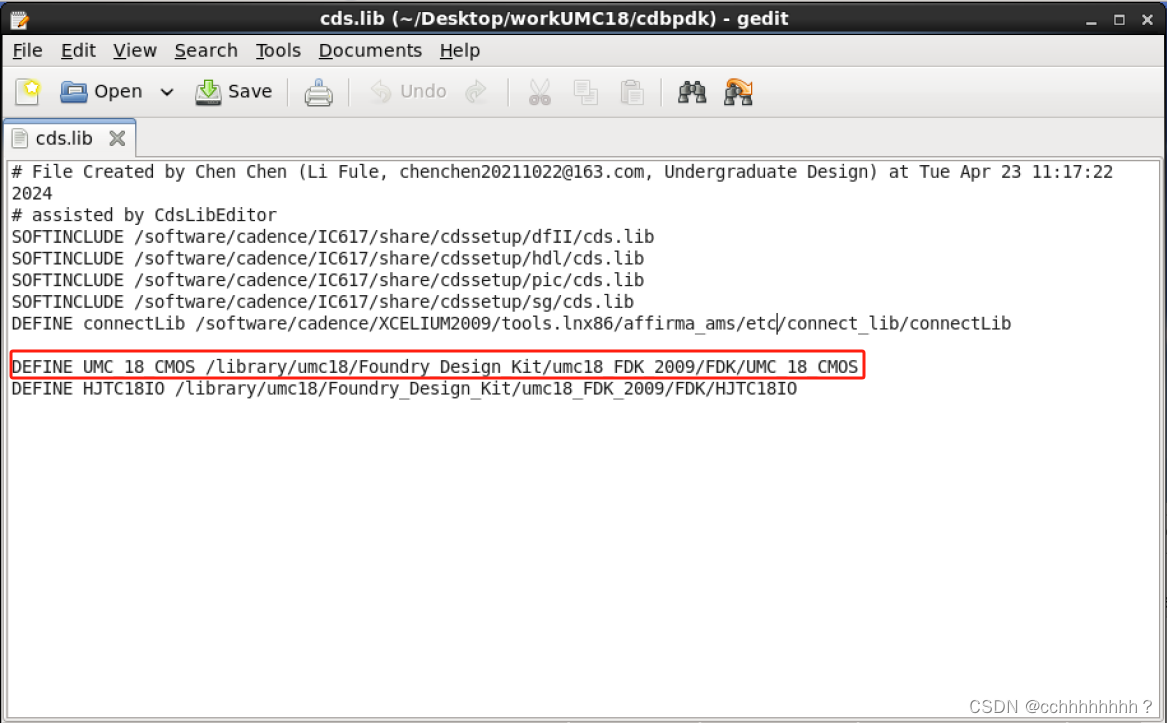

1.先把工艺库转oa格式。

新建一个文件夹(cdbpdk),里面包含cds.lib文件,cds.lib文件中包含cdb工艺库路径。

新建一个文件夹(OA),用于存转换后的oa格式的工艺库。

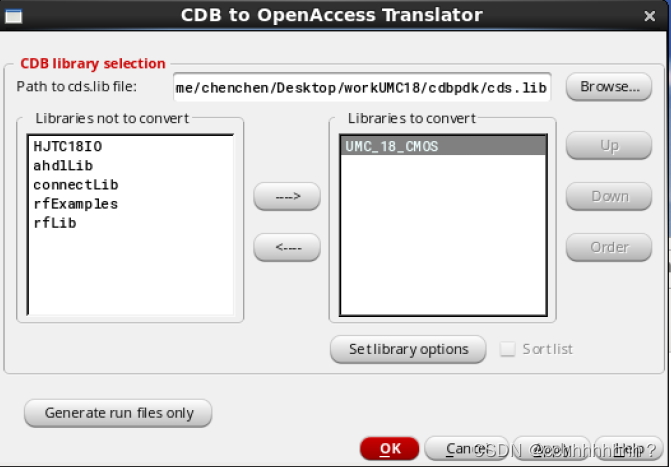

在OA文件夹下启动ic617(virtouso 617版本)。点击tools-conversion toolbox-cdb to openaccess translator。

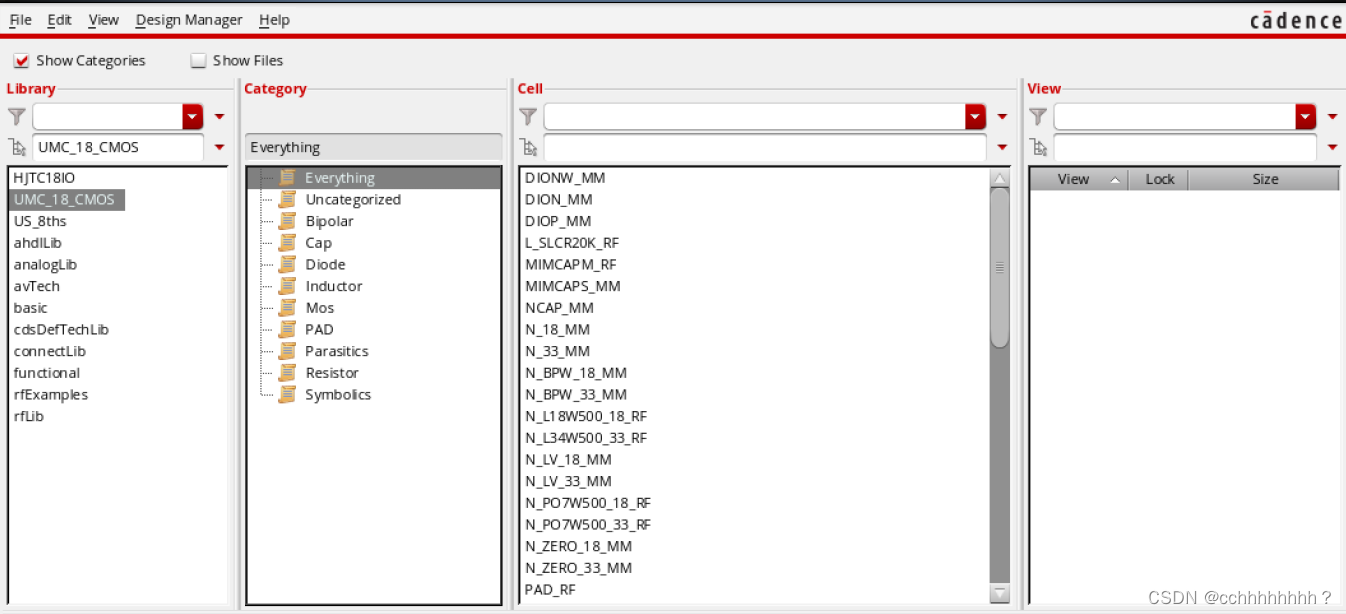

选中cdbpdk路径下的cds.lib文件,选中工艺库文件进行转换UMC_18_CMOS。点击OK。转换完成后,可以看到在library manager中出现了UMC_18_CMOS的工艺库

2.把设计转为OA格式。

在确保你当前cadence的运行路径下的cds.lib文件中包含oa格式的工艺库之后。再新建一个文件夹,里面包含cds.lib,cds.lib文件中有你要转的设计的路径。

首先在设计库目录下运行find . -name "*cdslck*" -exec rm -f {} \;把设计目录中的cdslck文件全部删除。

然后再tools-conversion toolbox-cdb to openaccess translator。类似的再进行一次转换。

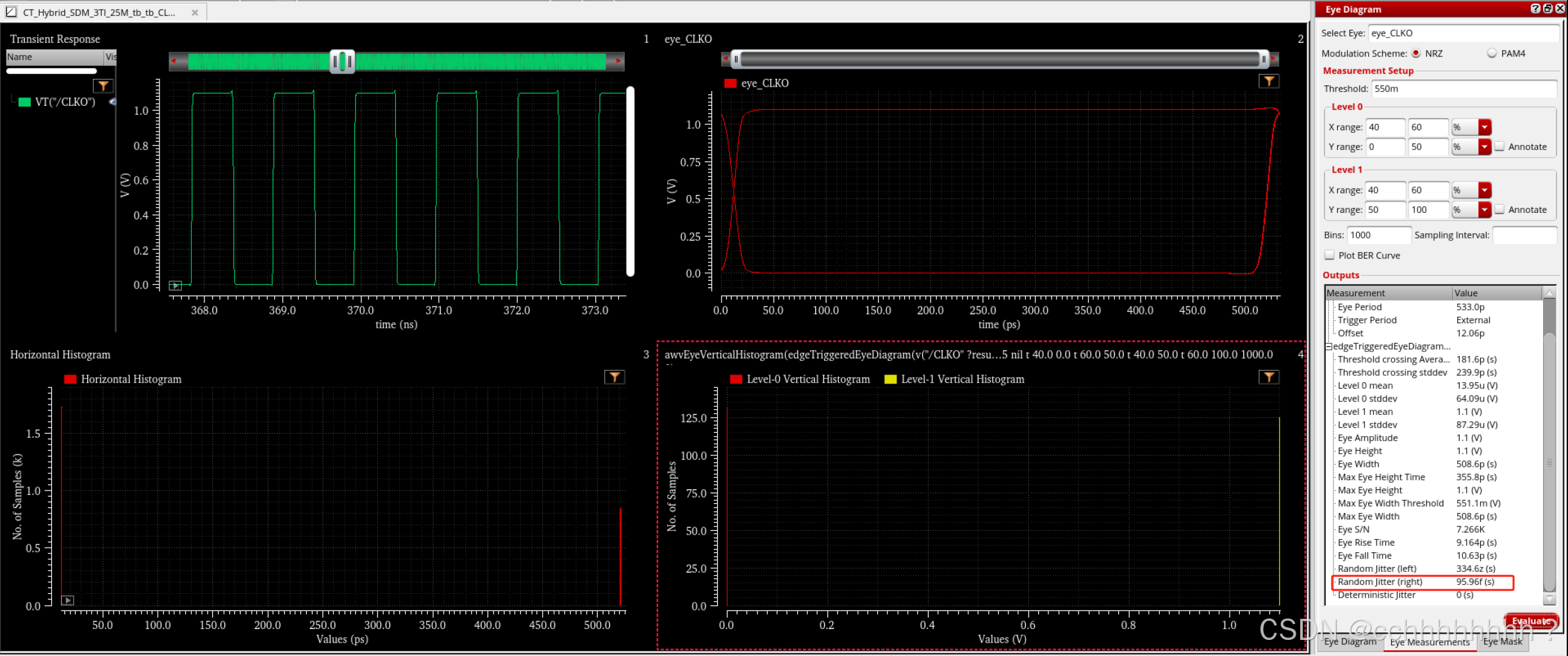

1、tran带noise仿真足够的周期数,周期数不够可能电路没有建立好,同时周期数会影响jitter计算的置信度

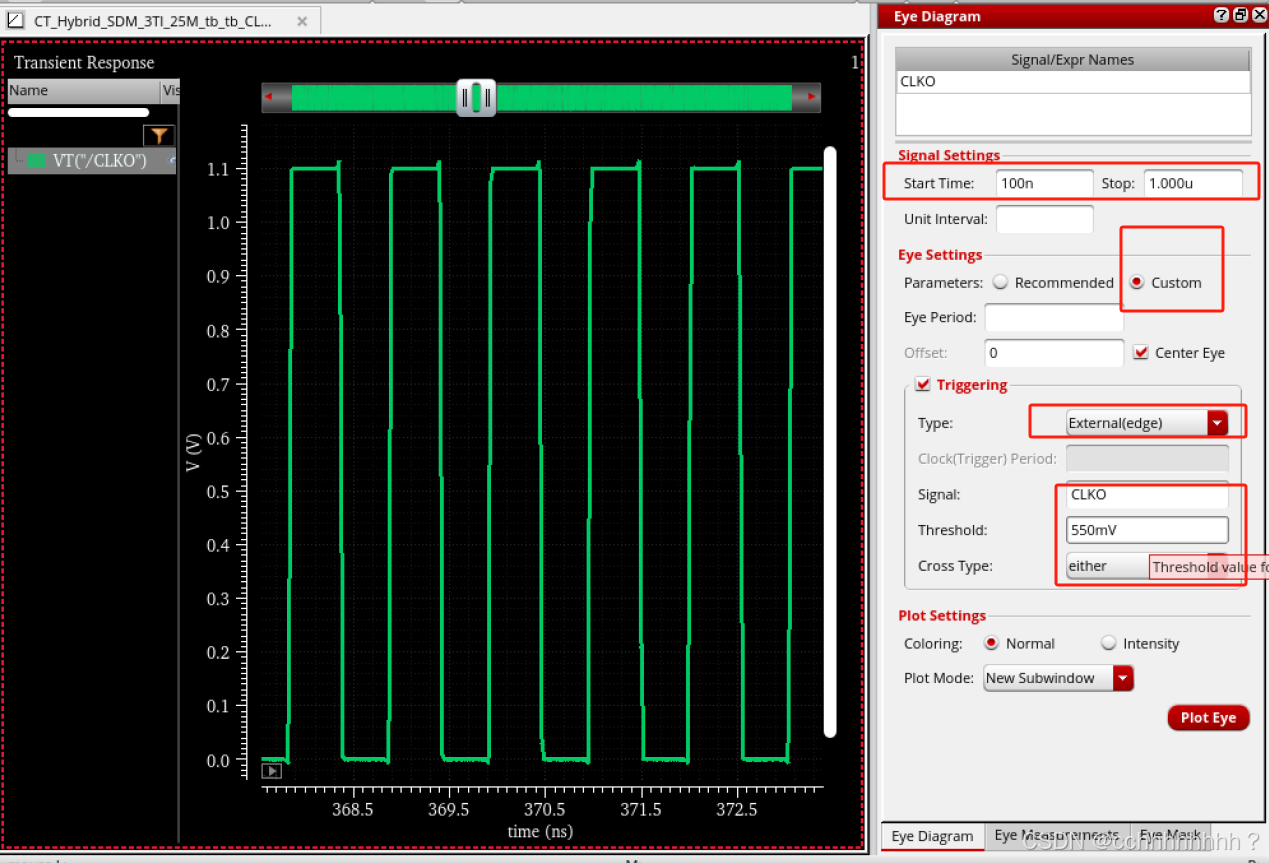

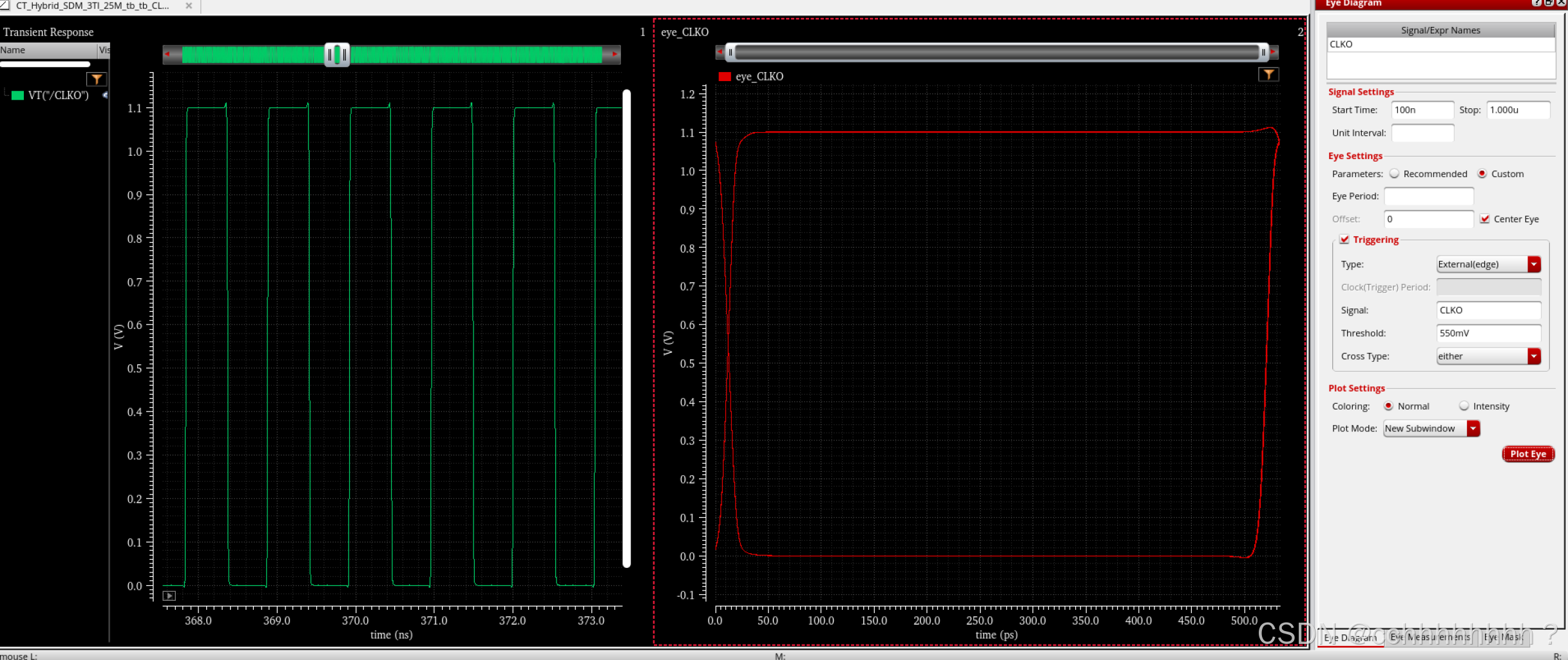

2、波形窗口measurement-eye diagram,并进行如下设置,点击plot eye,threshold为clk摆幅的一半。

3、点击右下角的eye measurement,选择刚刚画的眼,填入threshold,bins多填一点。即可得到random jitter(因为左侧它自动对齐了所以jitter几乎为0,要想换个edge看,就在cross type选)。

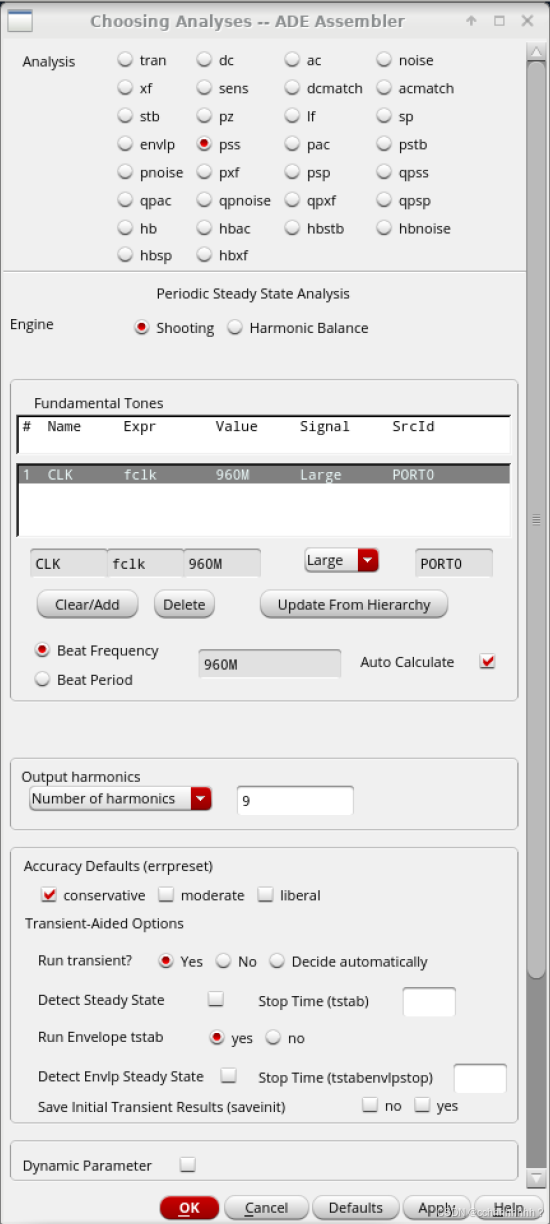

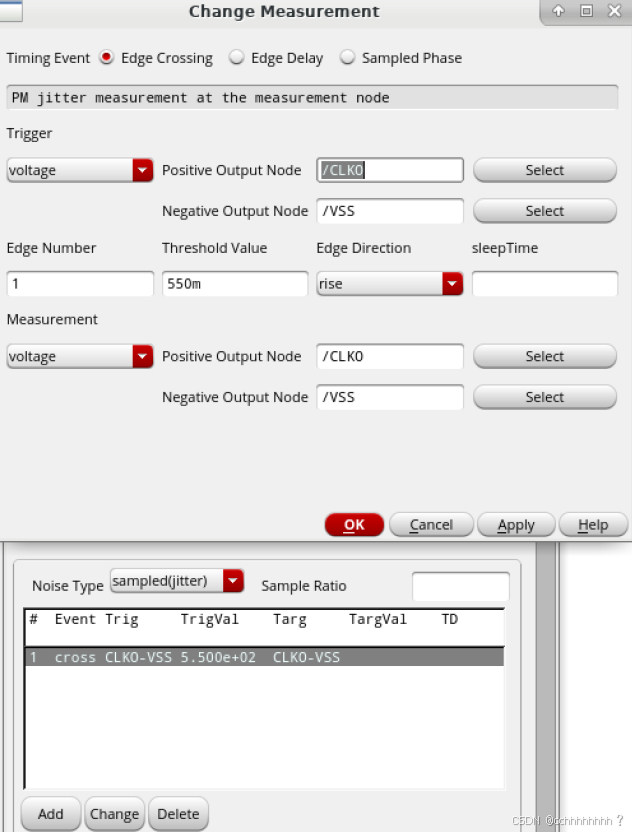

1、设置pss仿真

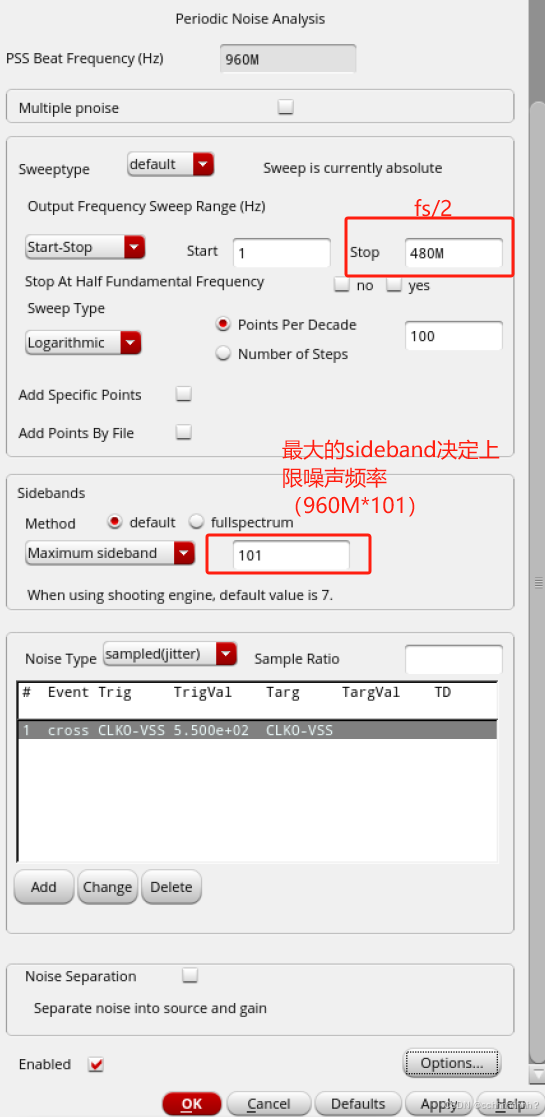

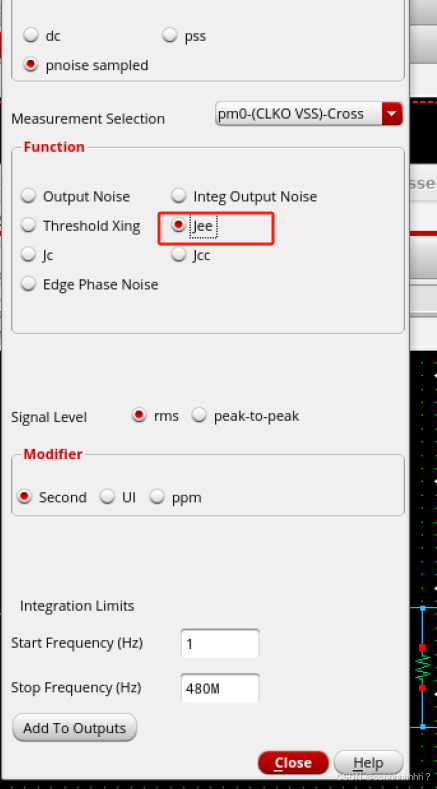

2、设置pnoise

trigger是时钟信号,measurement也是时钟信号

3、查看输出

pss+pnoise详解 https://blog.csdn.net/weixin_42221495/article/details/135466315

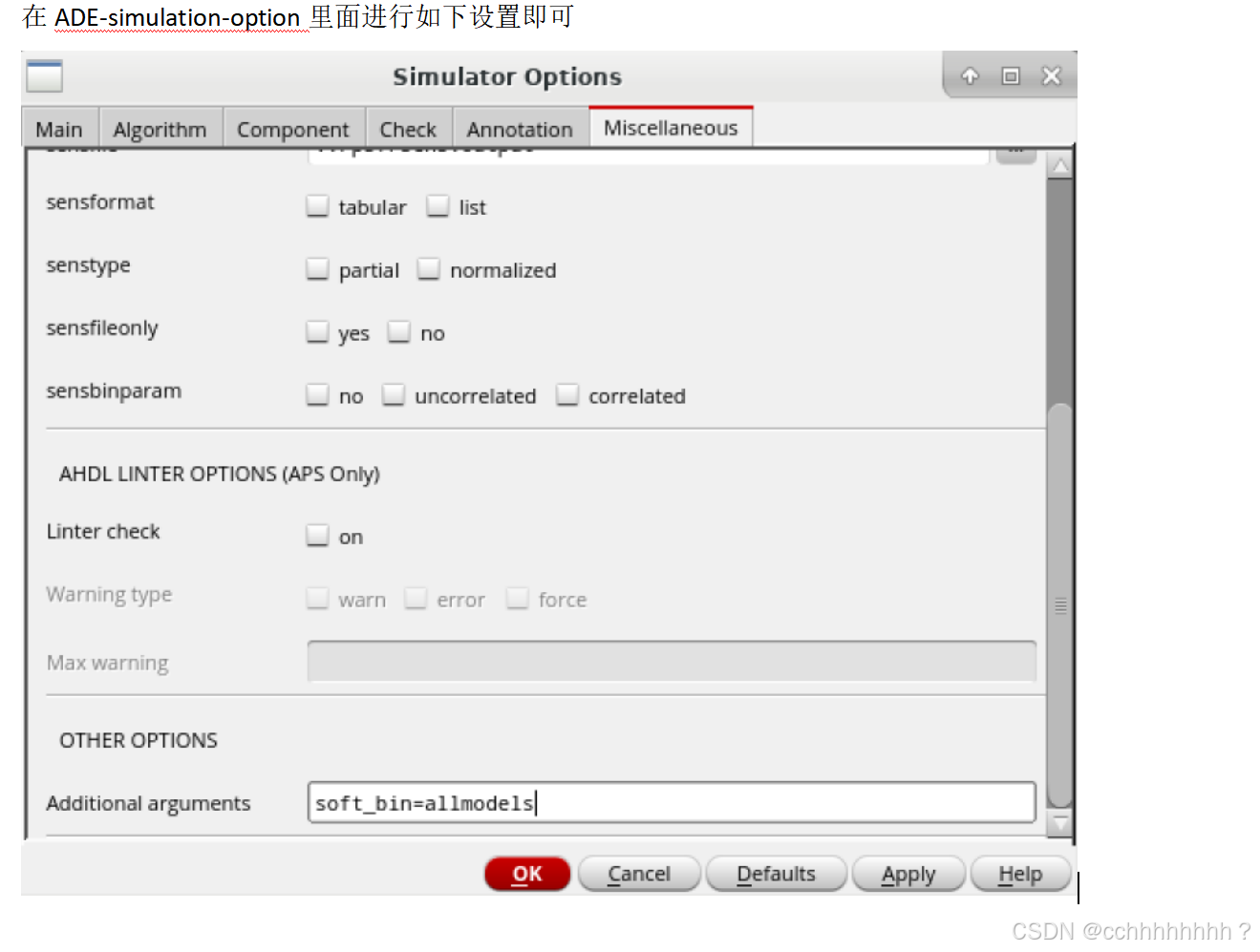

1.无法仿真,仿真就报错:Error found by spectre during initial setup. ERROR(CMI-2440):"/process/tsmc/CLN28HPC+/TSMCHOME/PDK/PDK1 _elk v1d8_3.scs ”53092: MO: The length, width, or area of the instance does not fit the given lmax-lmin, wmax-wmin, or areamax-areamin range for any mo

解决:

1.服务器和本地电脑之间无法直接复制,在terminal中输入vncconfig&,在那个小窗口不被关掉期间,都可以复制。

2.在 terminal 中运行:find . -name "*cdslck*" -exec rm -f {} \;

或者: rm 'find . -name "*cdslck*"' 删除所有的cdslck文件。

3.layout插入instance的时候,instance的版图离鼠标很远。原因是instance的版图没有画在版图的中心点上。改变一下中心点位置即可:edit-advanced-move origin

4. .cdsinit如果在本地目录有,就不会加载根目录的cdsinit,所以有些软件例如calibre,就不会给你加载,所以想自己配置cdsintit文件就要先把根目录下的复制过来,再进行配置。

5. 快速建立symbol,参考快速建立symbol但是至今用shift n添加不太行,得复制那个橙色的。另外在cdf里的设置也不可或缺。并且在调用时,需要增加user property-netSet-vdd以及vss,来和inheritvdd vss对应。

6. simulation文件太多太大,如何快速删除,cd到simulation路径:执行命令du -h --max -depth=1 | sort -rh | head -n 10,只寻找当前目录下第一层目录,并从大到小列出前10个。

7. linux系统对比文件,bcompare &进入GUI或者bcompare pathA pathB对比路径分别为A B的两个文件。

8. 获得别人的tb,先检查温度,先检查温度。

9. 浮空的电容节点一定要设置initial condition。可能前仿网表没问题,后仿网表会突然出现奇怪的问题,仿真器之前收敛的节点的初始电压的被后仿网表冲掉了。

10.lib库过多分类管理,先新建一个新的库(新建文件夹/new lib均可以),再 写入ASSIGN xxx COMBINE lib1 lib2 lib3,就把lib1 lib2 lib3放到一个路径下了

未完待续…

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删