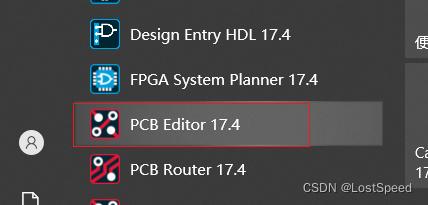

用 Padstack Editor 17.4 + PCB Editor 17.4 做封装已经试过了。

用 Footprint Expert PRO 22 做封装已经试过了。

这2种都是自己手工做封装,效率高低不同。

对于实在没有的封装(非标,或者只有封装尺寸文档),才用这2种方法。

还有一种是用现成的库(e.g. 力创EDA导出的库 或者 其他EDA软件导出的库),导入到cadence SPB17.4中,这种场景比例很高。

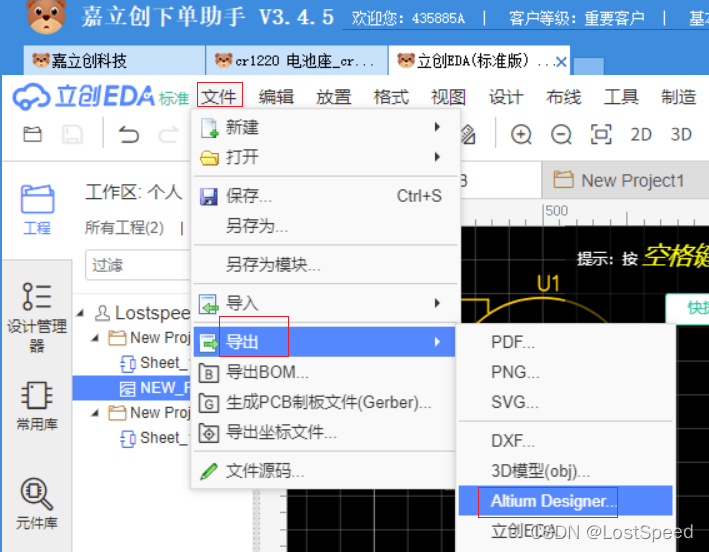

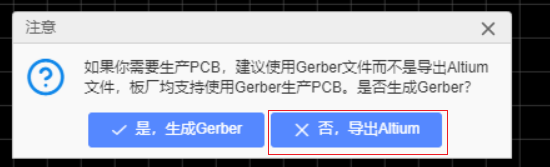

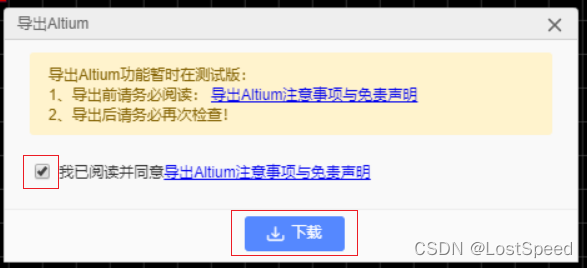

现在买料都在力创上,大部分料,力创都提供封装库,先尝试将力创库导入cadence SPB17.4试试。

需要用到的软件 :

力创EDA在线版

AD2022 SP1

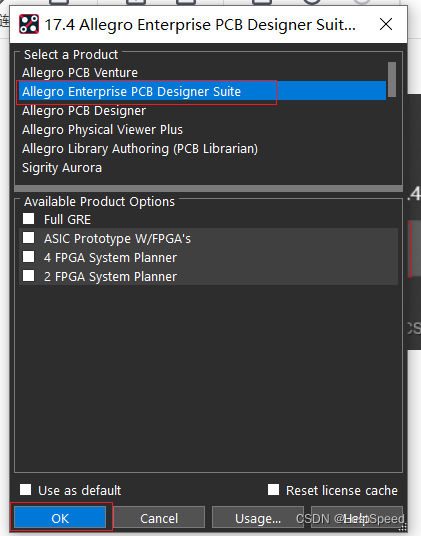

cadence SPB 17.4

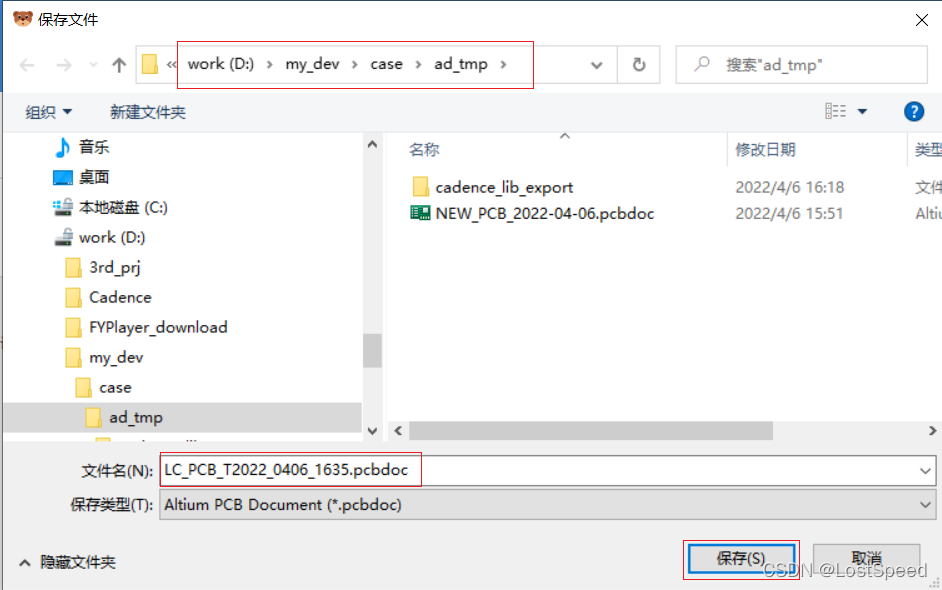

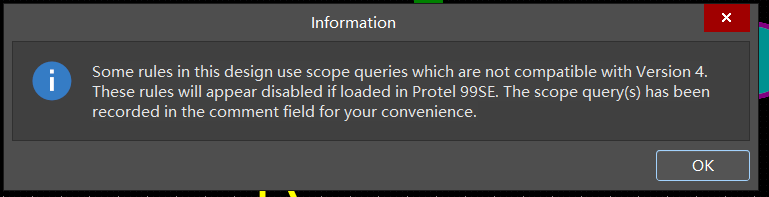

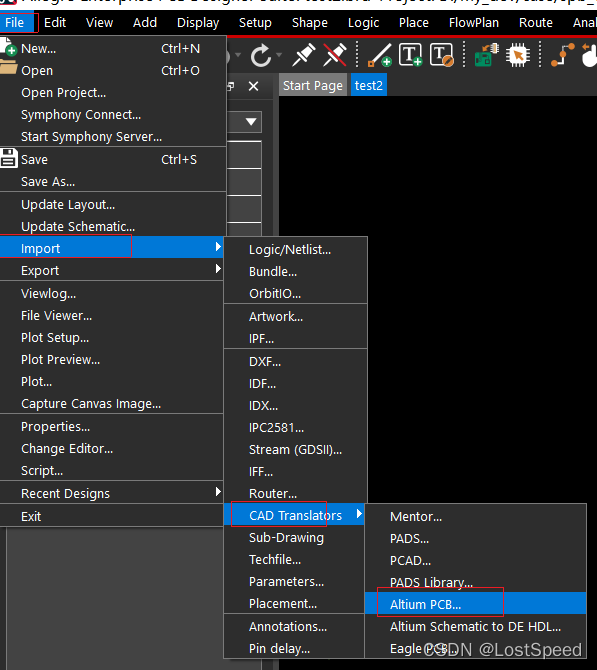

做这步的原因: cadence SPB不支持力创导出的AD文件,只支持AD的ascii格式的PCB文件。cadence官方文档有说明 :https://www.gofarlic.com\Cadence\SPB_17.4\share\pcb\translators\ help \altium2pcb.pdf

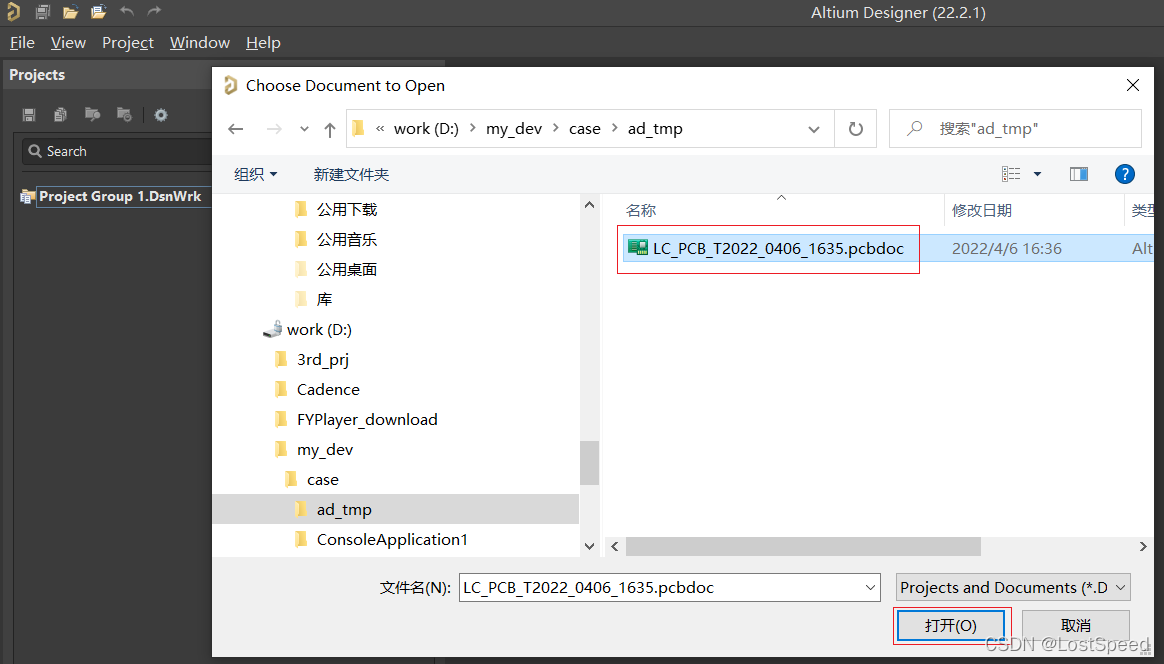

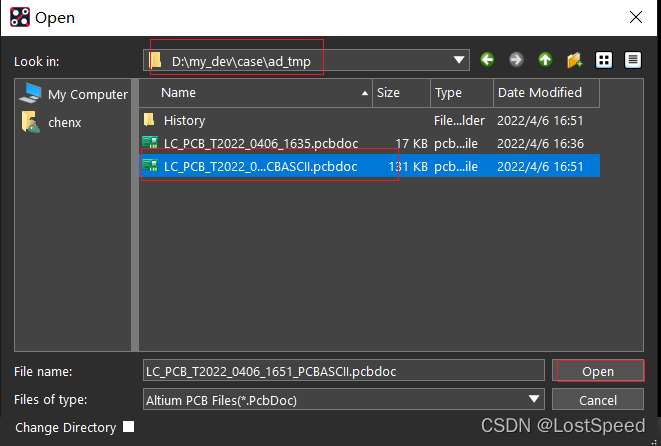

用AD2022打开力创EDA导出的AD PCB

用的AD版本是 22.2.1.43

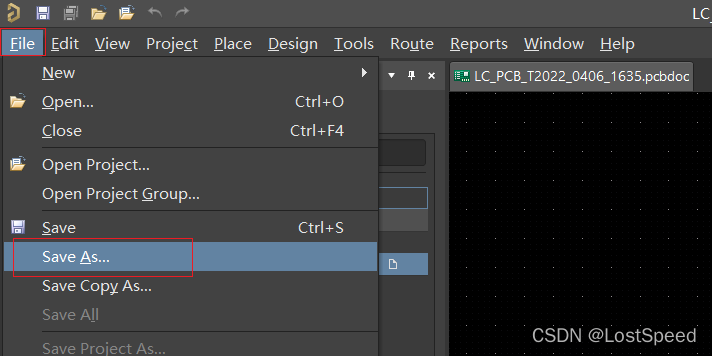

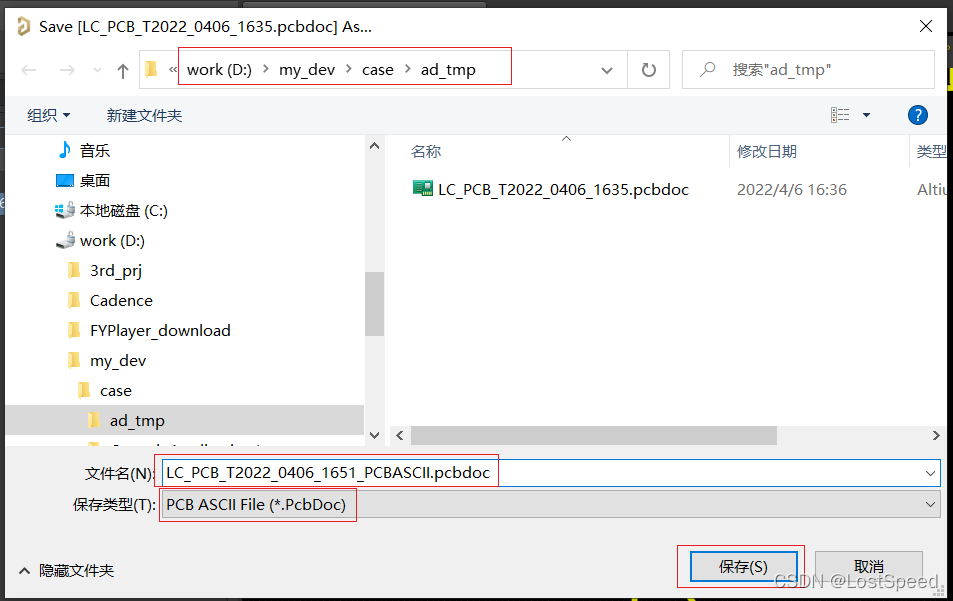

另存为AD PCB ASCII文件之后,会有如下提示。

这个提示说, 这个PCB文件中的一些特性在Protel 99SE中不支持。

估计AD PCB Ascii格式的文件,是给protel 99SE用的。也可以看出,AD PCB ASCII 格式,是AD能导出的最低版本的PCB格式。

不用管这个提示。

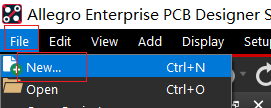

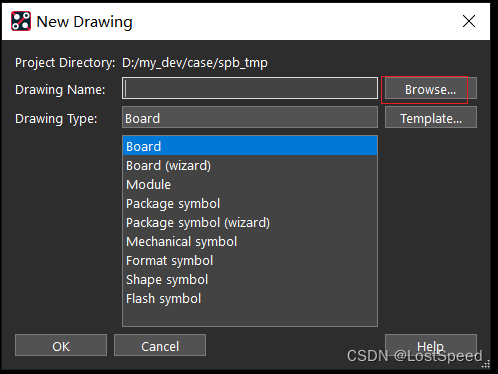

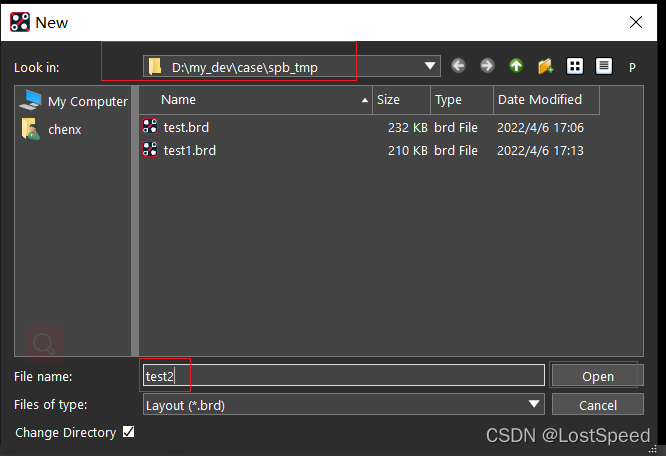

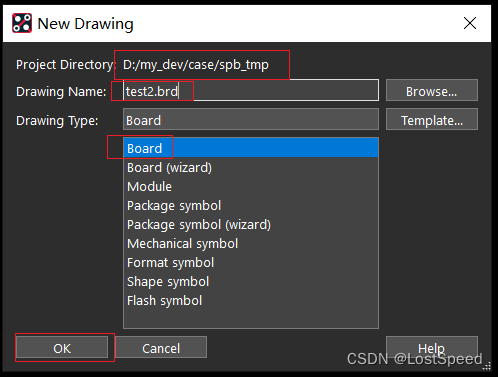

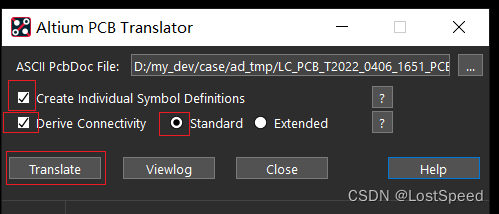

新建板子工程

默认单选是标准

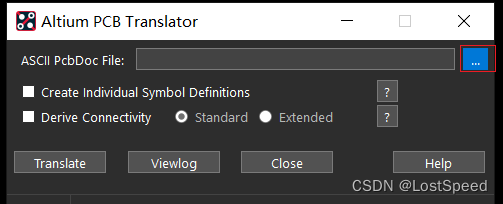

根据altium2pcb.pdf中的建议,多勾上2个选项好一些,如下

点击转换按钮,开始导入AD ASCII PCB 到cadence SPB17.4

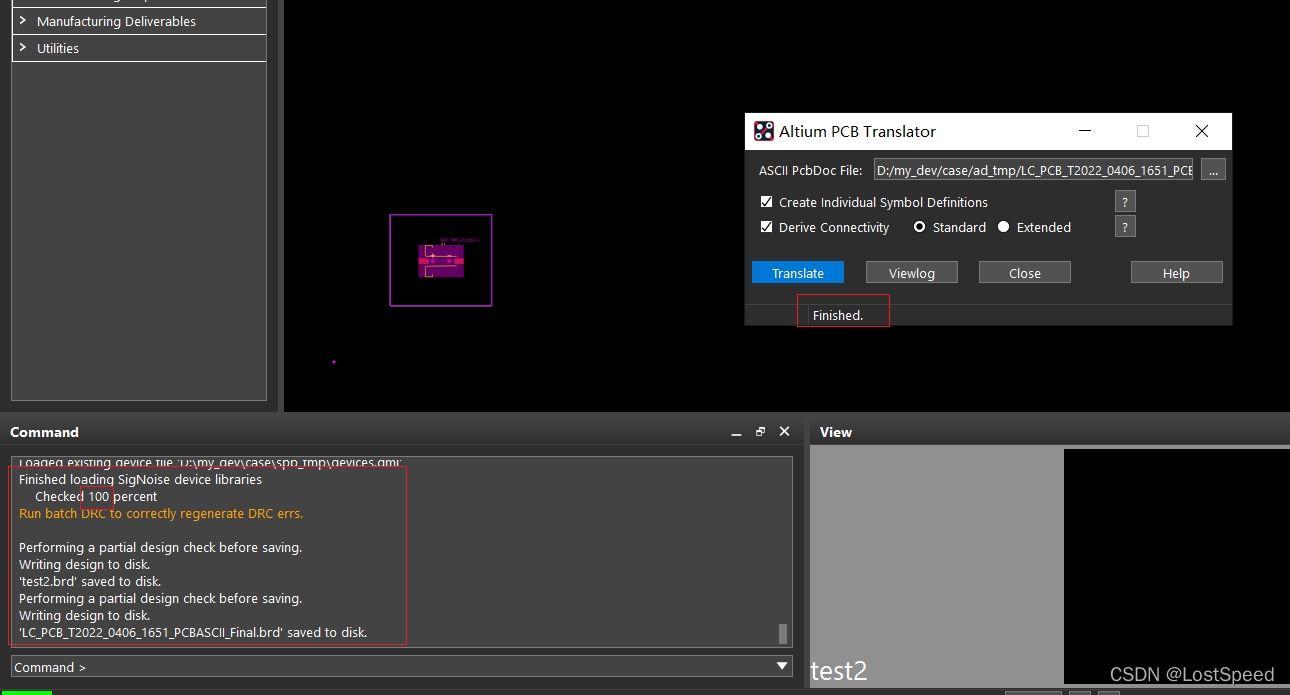

如果没错误,左下角的提示 信息 能看到。

如果有错误,就要检查是否AD导出的是ASCII格式的PCB(我只遇到这一种错误,因为我开始直接导入了力创导出的AD PCB).

关掉导入转换 对话框 。

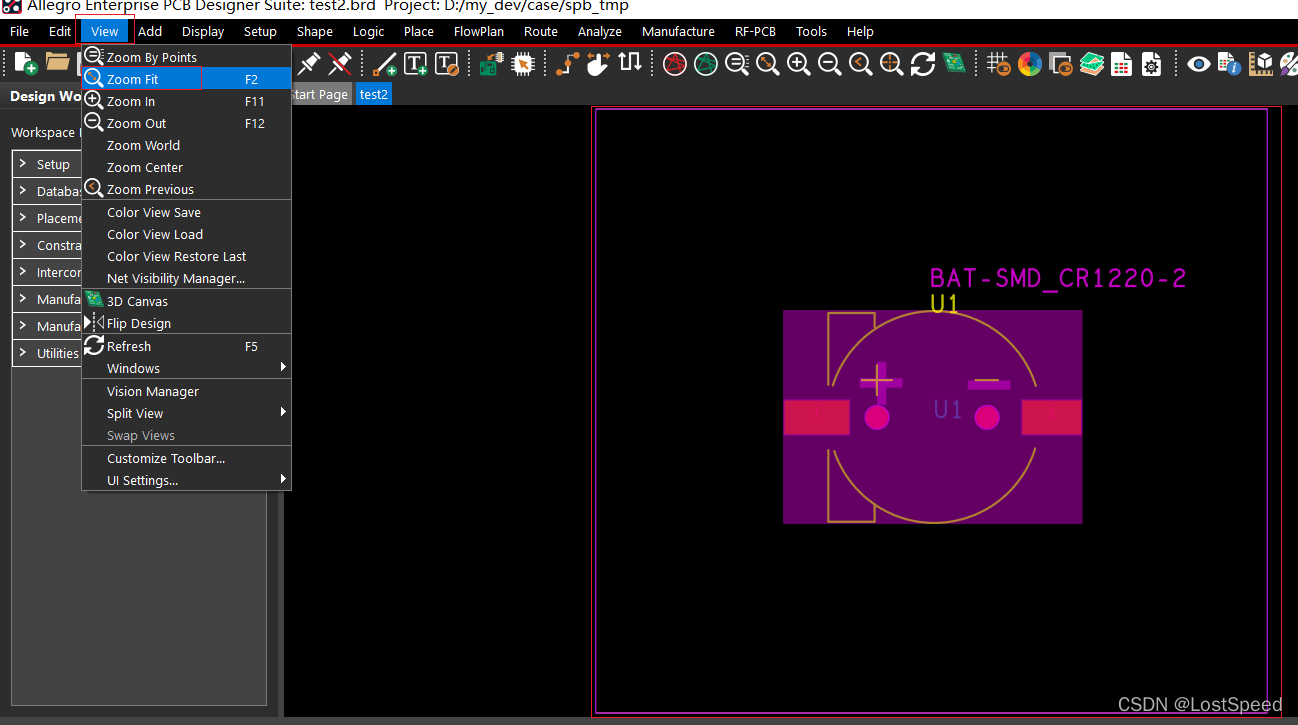

按F2, 缩放导入后的PCB便于查看。

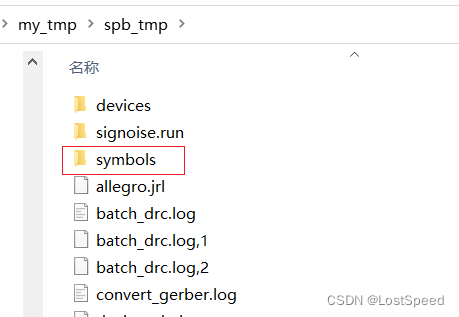

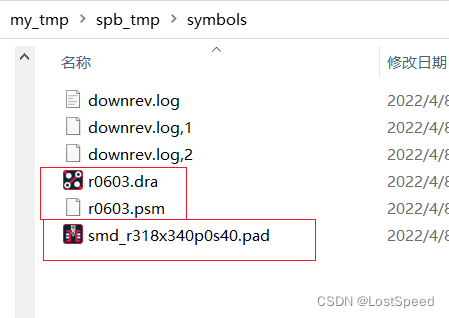

如果导入的PCB上只有一个元件的话,这时在工程目录symbols下,已经可以看到库和焊盘文件,可以直接用(手工拷贝库文件到库目录),不用另外导出库文件。

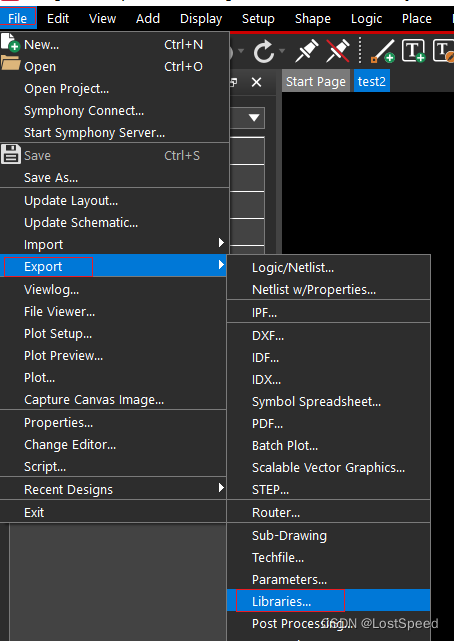

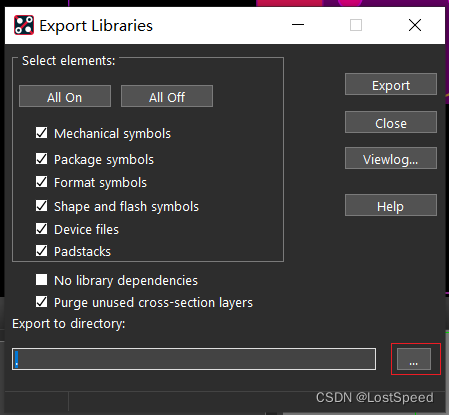

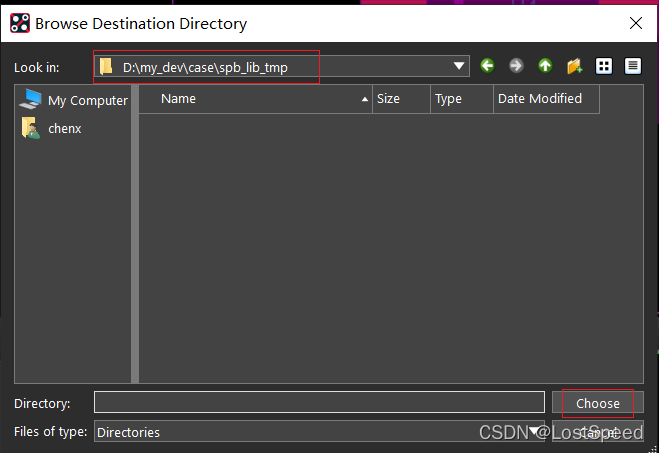

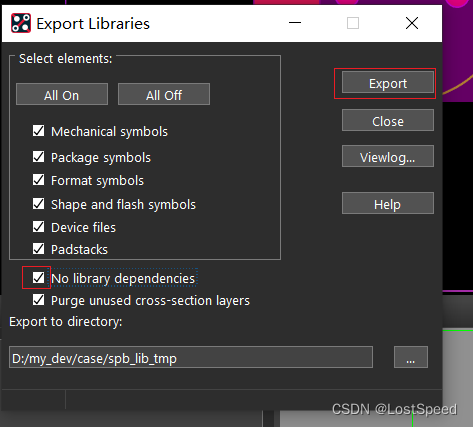

指定导出的库到单独的临时目录

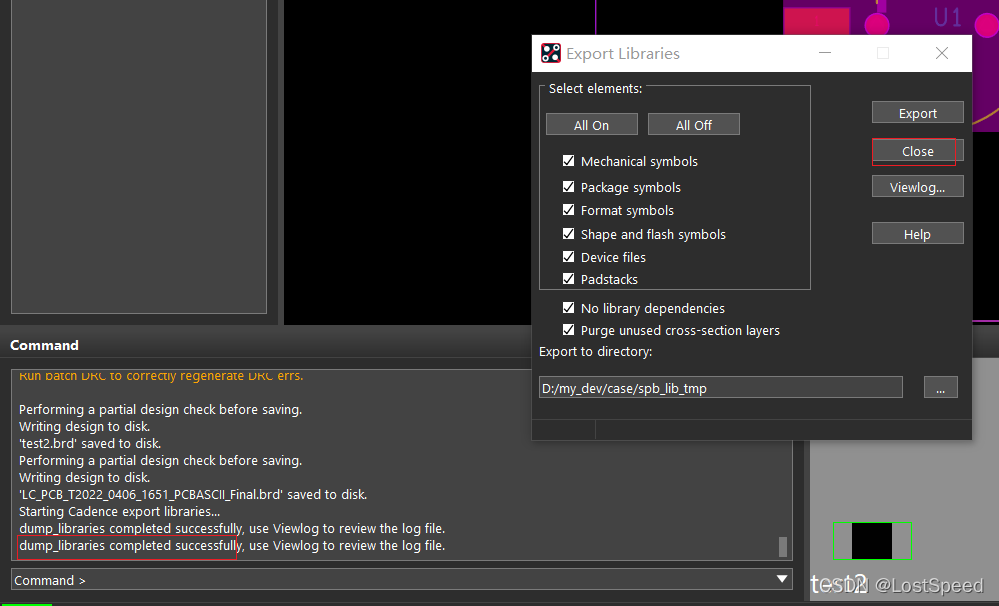

导出成功,关掉导出对话框

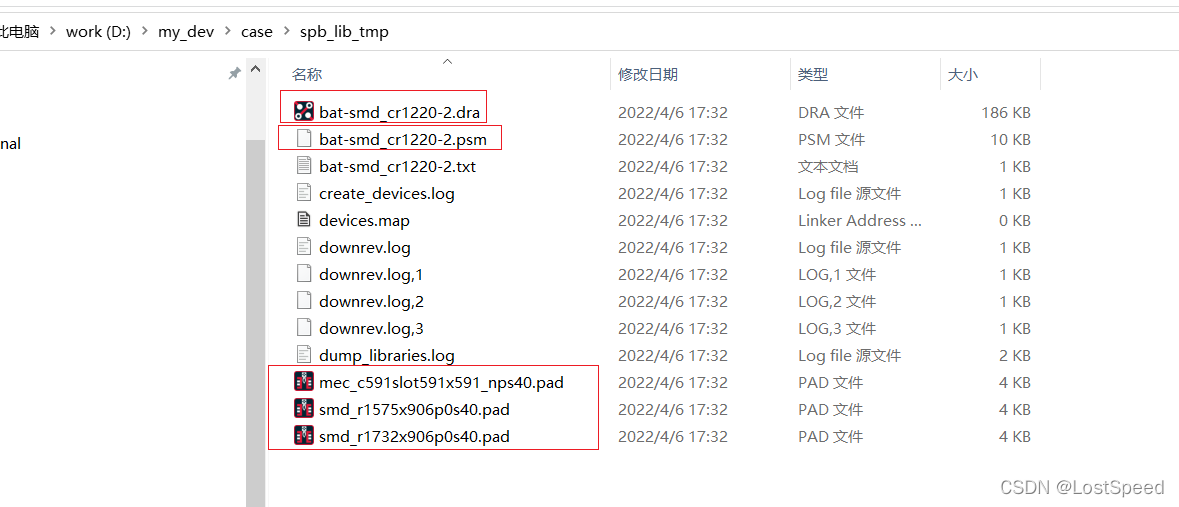

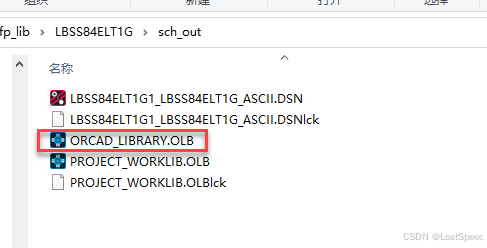

去库临时导出目录看一下

看到库导出目录中有3 类 文件

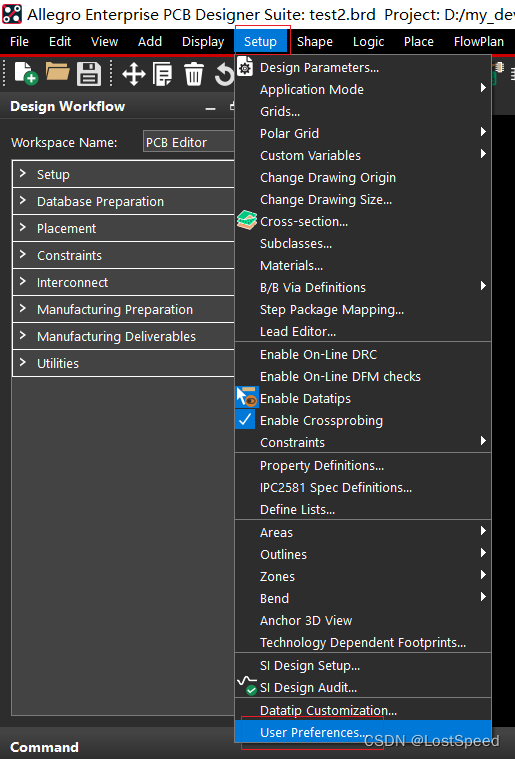

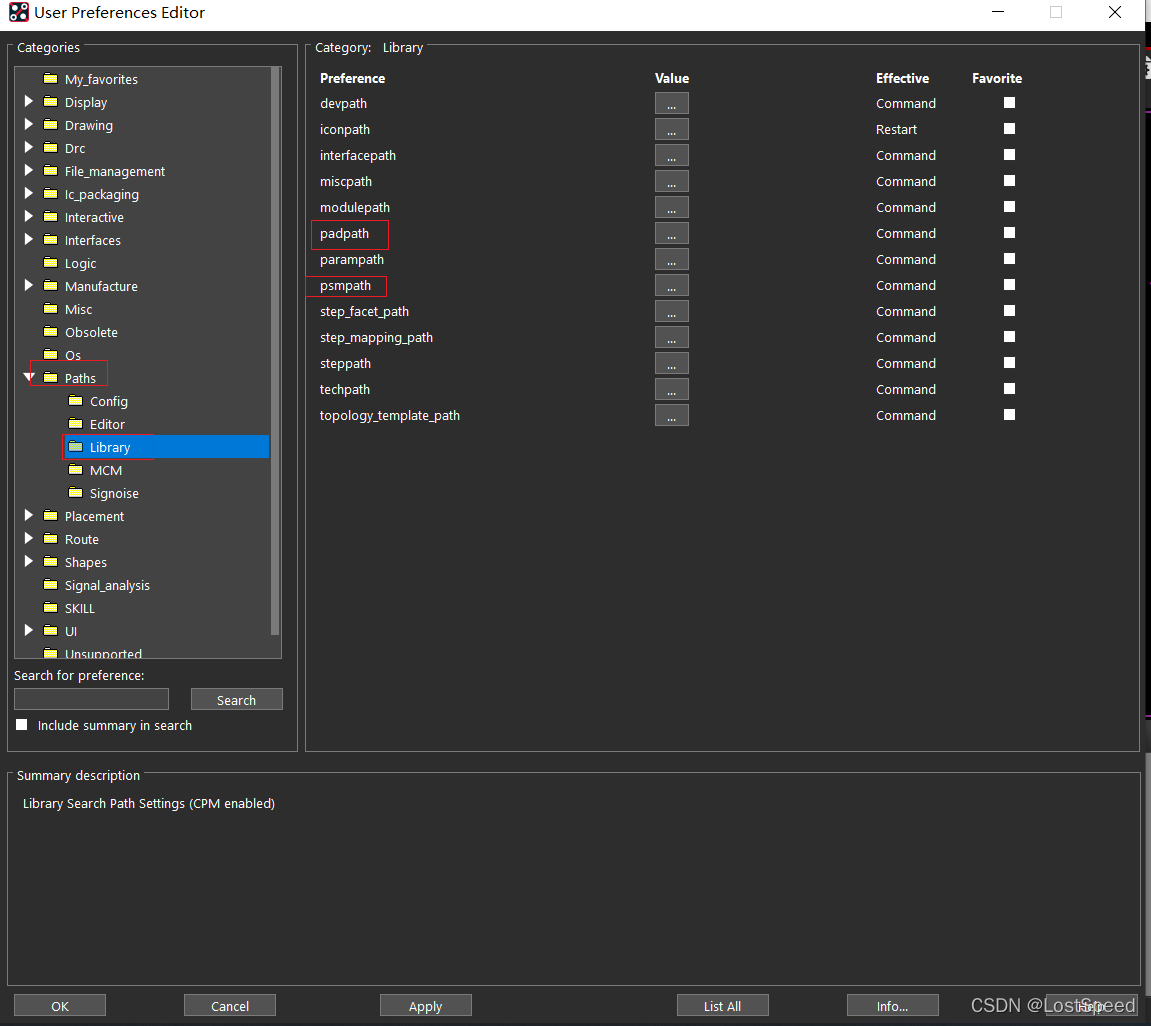

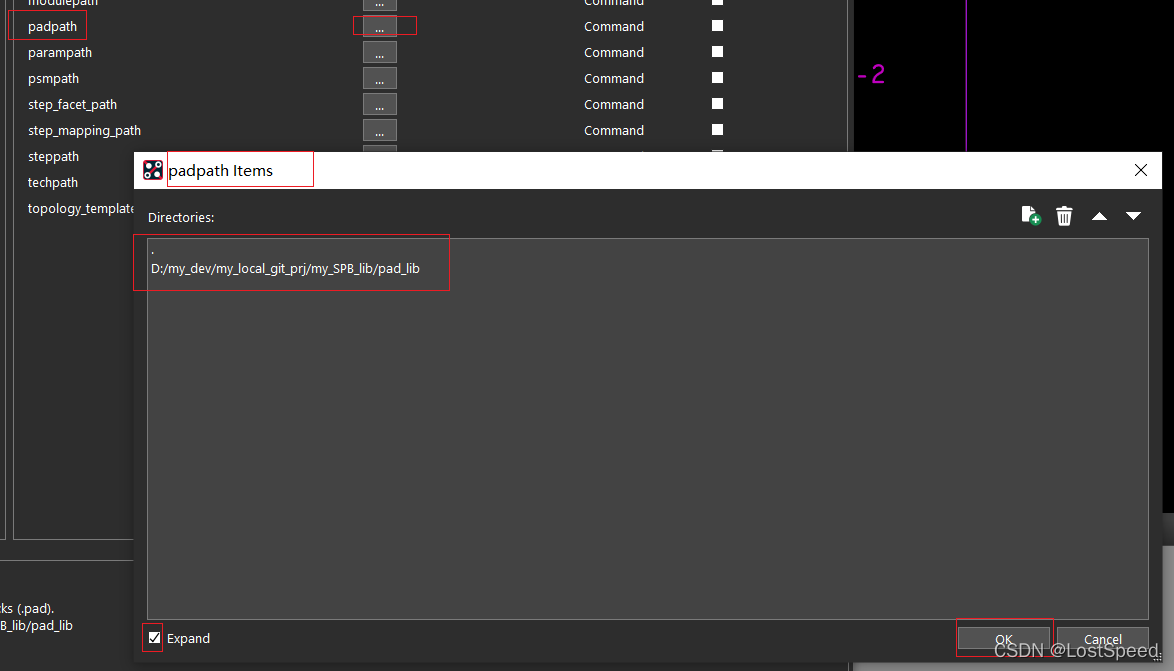

确认自己的SPB的库路径配置

确定库文件路径, PSM文件路径,焊盘文件路径。

焊盘文件路径

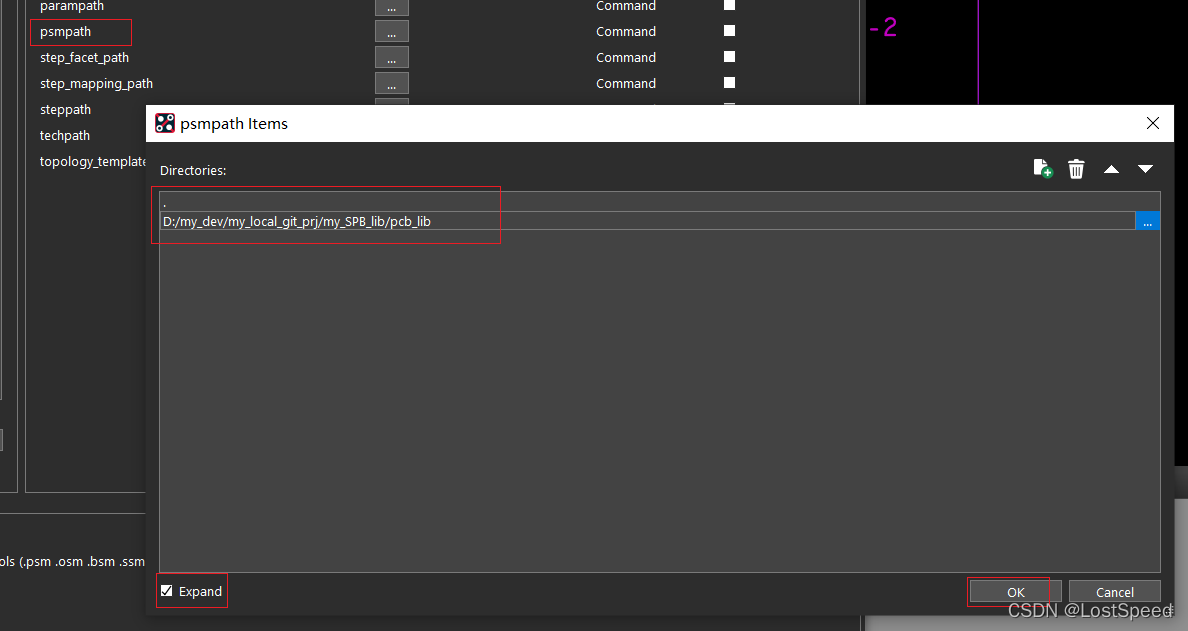

PSM文件路径

库文件.dra在cadence中,没有规定有路径变量,和PSM文件放在一起就行。

将临时目录中的*.dra 和 .psm 拷贝到自己的 PSM文件路径中。

将临时目录中的.pad拷贝到自己的PAD文件路径中。

因为我们设置路径时,除了绝对路径,还设置了. 路径。

将导出的元件封装的.dra, .psm, .pad全部拷贝到PSM文件路径中也是可以的。

但是分别拷贝到PSM文件路径和PAD文件路径中,以后维护方便些。

导入的库名称和库中放置的标识啥的,可能有不合适的。用PCB Editor打开导出的库,另存,可以改变.dra的名称. 如果打开.dra后,发现有啥不合适的,直接改,然后存盘就好。

退出dra封装文件的编辑,如果有洁癖,可以将封装文件位置中除了*.dra, *.psm之外的临时文件都删了。

因为我是先画的层次原理图,现在将封装之外的错误都消掉了。

我只需要换一个元件的封装,然后看看是否这个元件的封装错误没有了。就知道封装指定的是否合适。

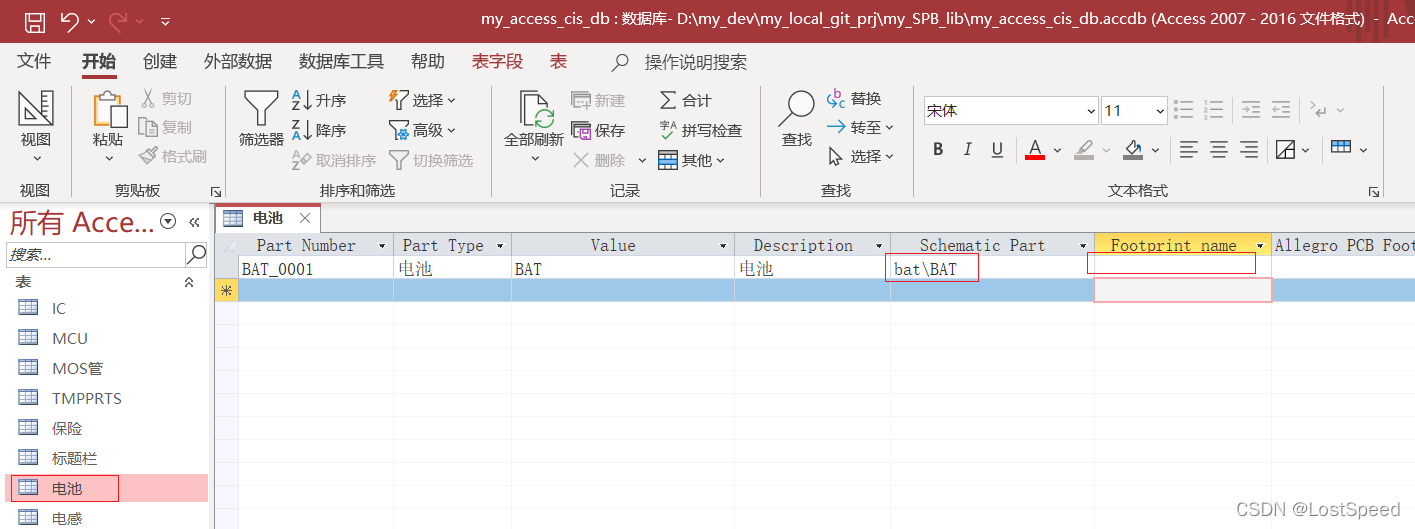

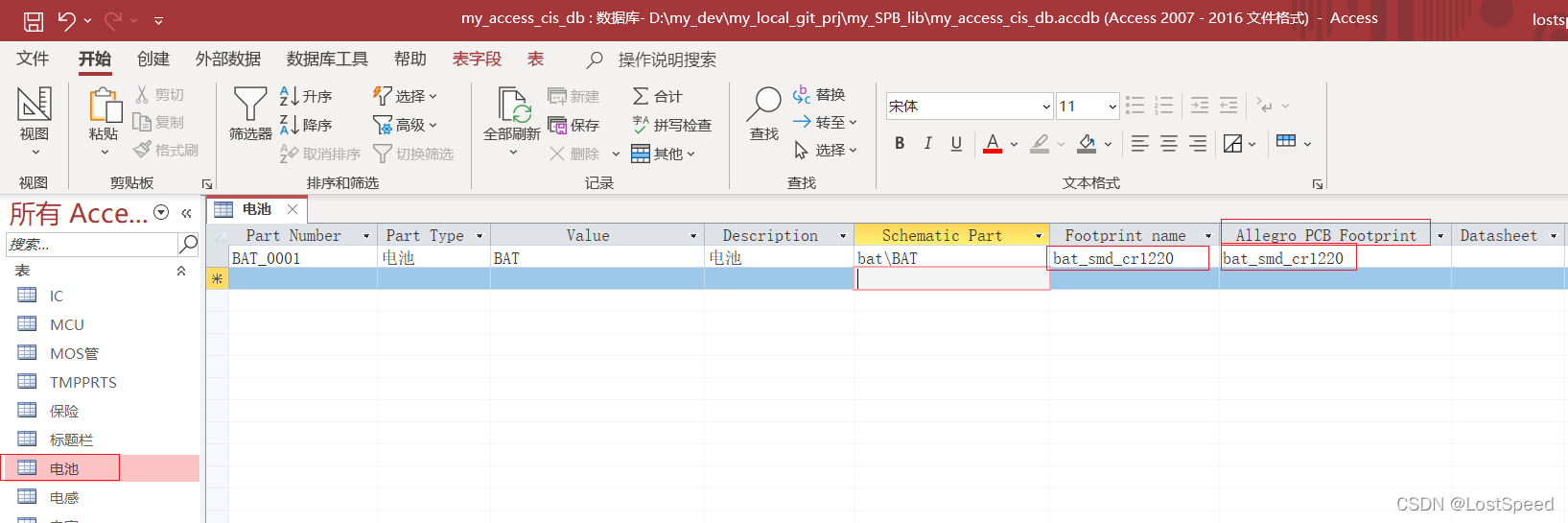

做了自己的CIS库,里面只有原理图器件名称,没有PCB元件封装名称

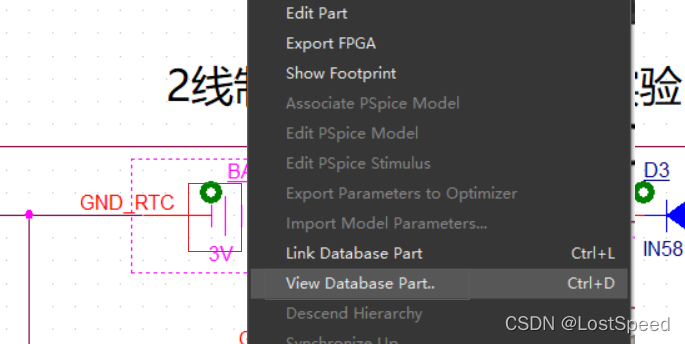

在原理图中,查看数据库元件属性,也看到是这样。

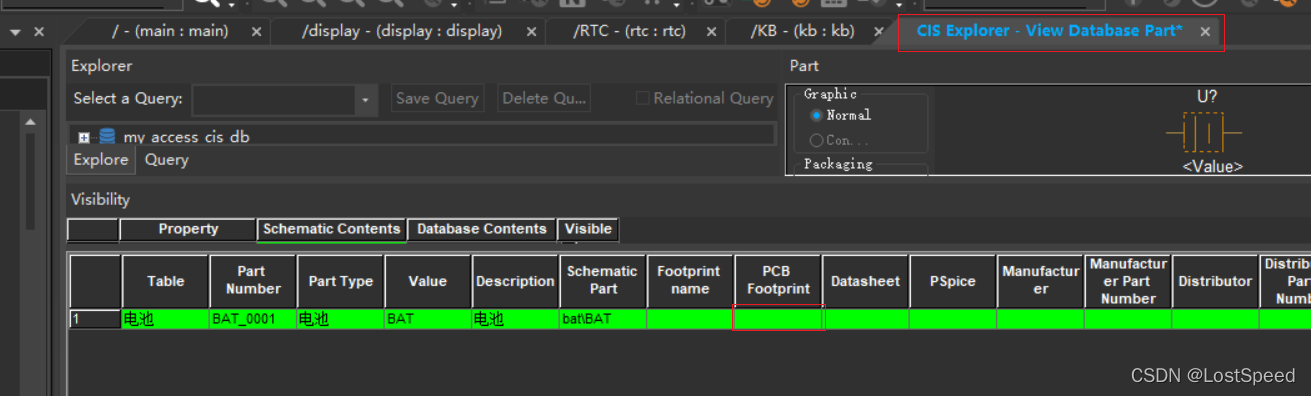

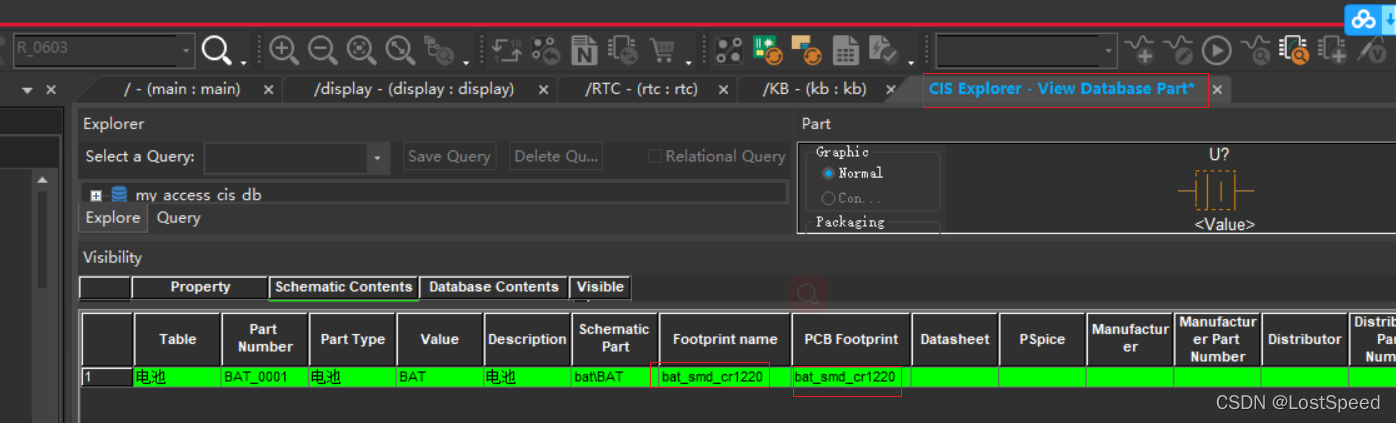

现在, 在CIS库中填入PCB元件封装名称(dra)和封装名称(用来出bom单的器件name)

在原理图中查看数据库元件,也有了封装名称

DRC,看看这个BAT1的位号,是否还有封装的报错?

还有封装找不到的错误。

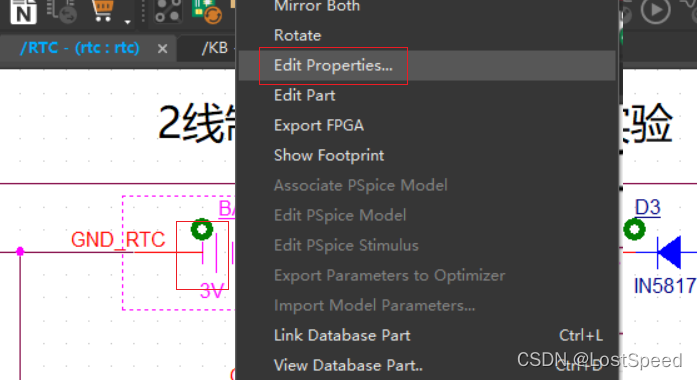

编辑这个元件的属性。

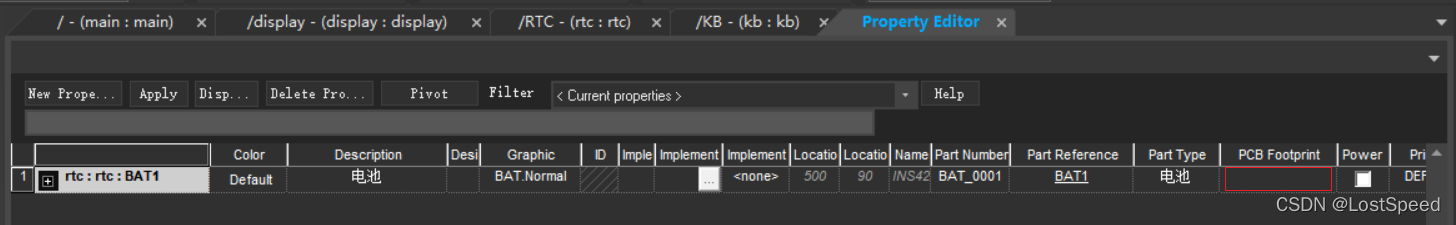

看到封装那里还是空的,说明需要更新元件库

更新元件库之后,封装还是空的。

重新从CIS库中摆一个元件。

摆放新的元件后,将新元件的位号,描述改为旧元件的值。将旧元件删掉,将新元件摆放到旧元件的位置,线都连接好。

再查看这个新数据库元件的属性,封装那里已经有了封装名称。

再DRC, 从DRC列表和drc文件中, 已经看不到BAT1这个元件有封装错误了。

那现在还有一个问题,我先画好了图,再弄的封装。如果等封装做好了,更新到了CIS数据库,在原理图上都要将CIS库元件都摆一遍,那受不了啊。

是不是要在capture中,将cis数据库更新一下才行?还是非要自己重新摆一下元件才行?那需要整下一个封装时,再验证这个问题。

又导入了一个力创封装

在导入封装前,做的DRC检查错误如下:

.drc文件中看到的报错信息

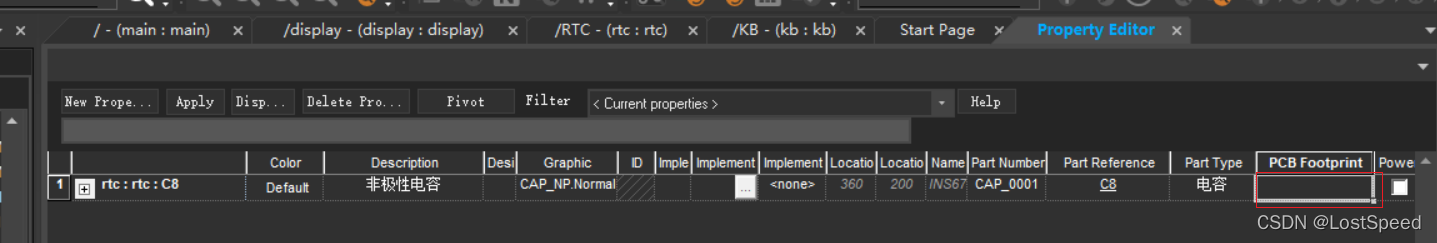

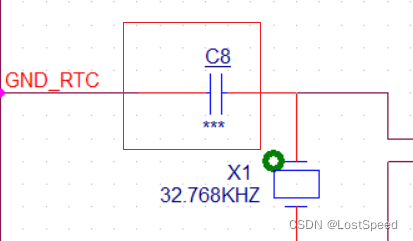

#101 ERROR(ORCAP-36002): Property "PCB Footprint" missing from instance C8: rtc, rtc (91.44, 50.80).

UI上DRC小绿环双击显示的报错信息

ERROR(ORCAP-36002)

ERROR(ORCAP-36002): Property "PCB Footprint" missing from instance C8: rtc, rtc (91.44, 50.80). RTC/C8: rtc, rtc (91.44, 50.80)

RTC/C8

因为在CIS库中的封装BOM名称和封装实体名称都没有

在accdb中填入封装BOM名称和封装实体名称,在C8上右击,选择查看数据库元件,已经显示有封装实体名称。

再次DRC. C8依然还是这个错误。

刷新Z键时的数据节点的类型信息和详细信息,再DRC, 还是不好使。

难道非要重新摆这个元件才行?这不科学啊, 谁会这么搞?

关掉capture, 重新打开后,DRC, 还是报错。

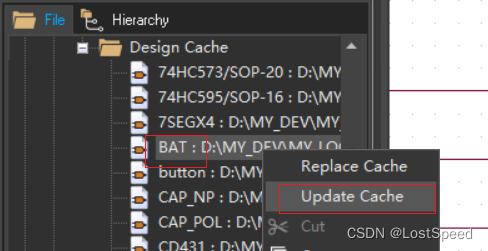

更新替换缓存,重新打开后,DRC, 还是报错。

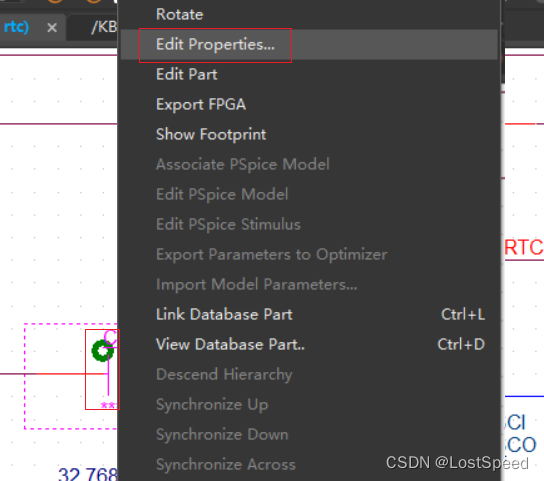

尝试查看元件属性

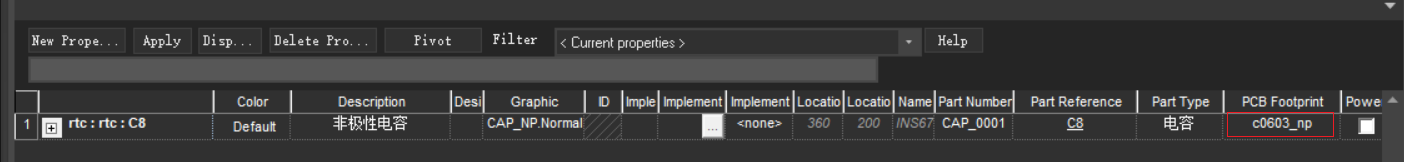

可以看到封装的实体名称为空,这就是原因。

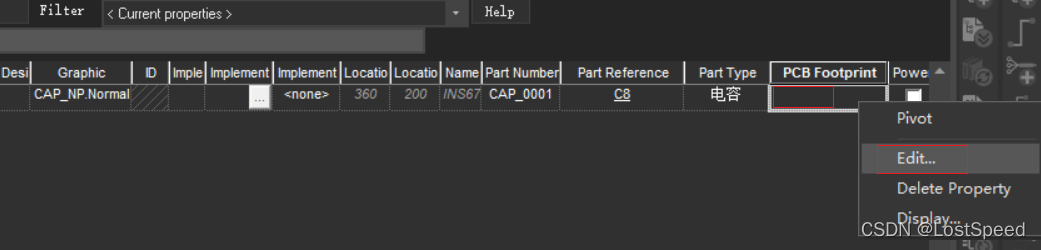

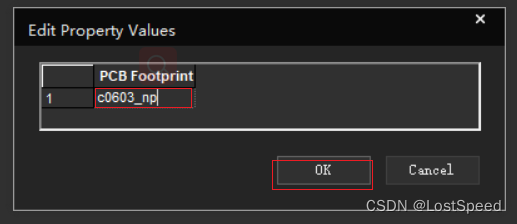

尝试编辑封装实体名称。

封装名称已经改过来了。

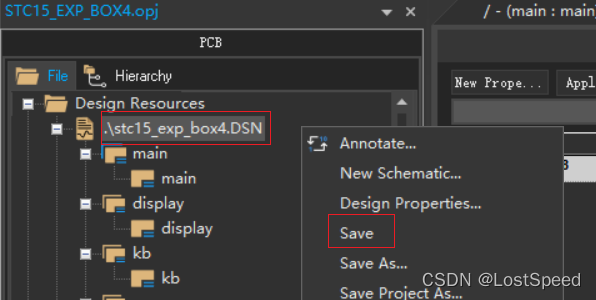

保存工程

再次DRC, C8这个元件没错误了。

由以上实验可以看出:

如果要更改原理图上的CIS库封装。要先在CIS库(.accdb)中填入新的封装名称,但是这个操作是给要新摆放的原理图CIS库器件用的。对已经画好的原理图器件不好使。

对于原理图上已经有的原理图CIS器件,要右击该元件,选择编辑属性。然后去编辑封装实体名称这个属性,才能更新为新封装。

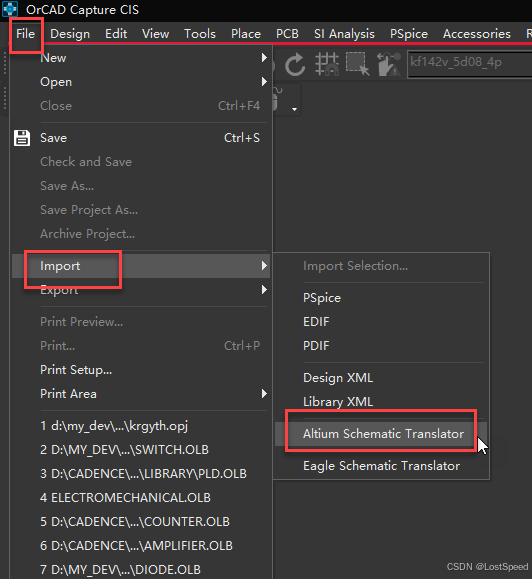

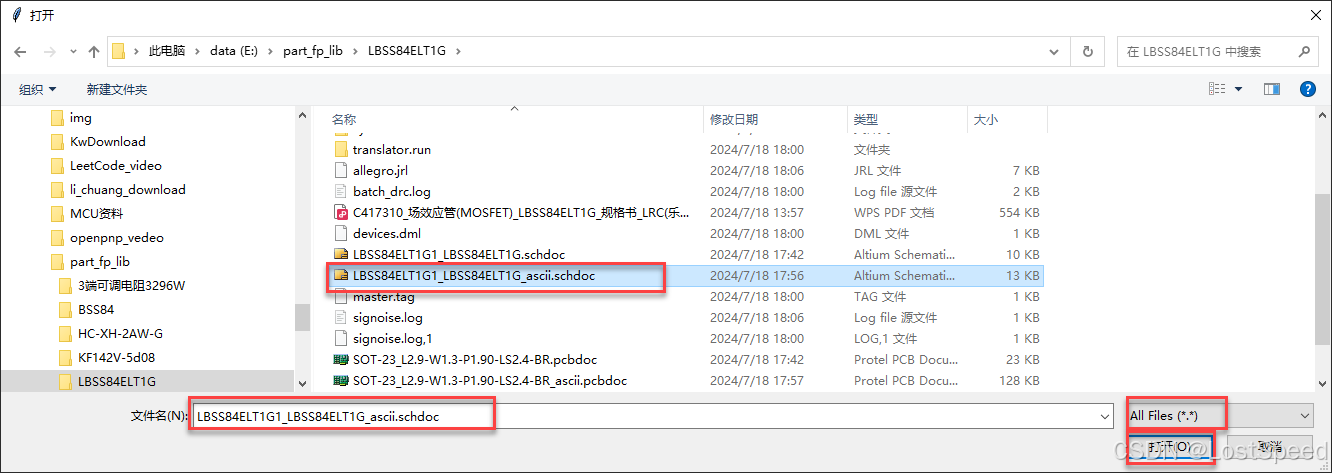

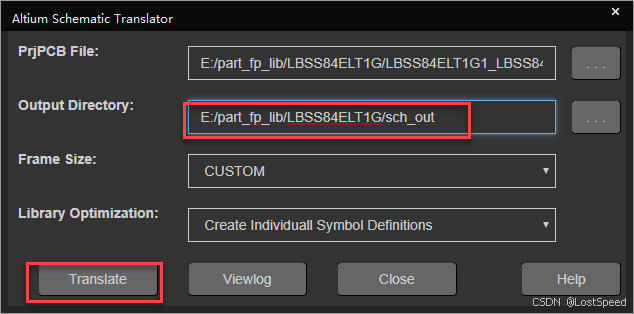

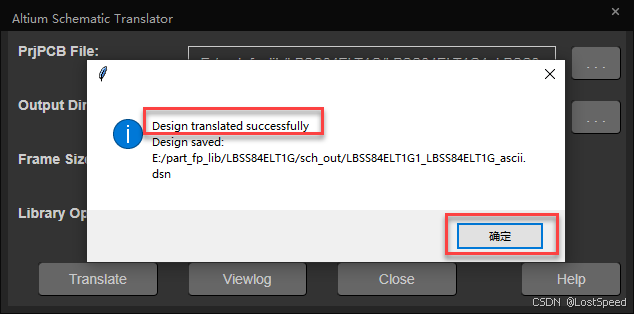

先将LC导出的AD原理图, 保存成ascii格式。

再用capture-cis导入。

刚进入capture-cis, 没有打开任何工程时,就可以导入AD格式的ascii原理图

这时,就可以将cadence生成的原理图库中的库元件拷贝出来,粘贴到自己的原理图库中。

试过了(2024/9/11), 从JLC导出的AD原理图,不需要再用AD另存为ascii格式的sch, 直接用SPB17.4就能导入。

不是所有的JLC导出的AD原理图都能直接用SPB17.4导入。

还是统一将JLC导出的.sch, .pcbdoc都用AD载入后导出为ascii格式后,再用SPB17.4导入靠谱一些。

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删