记录了一些自己在cadence仿真过程中出现的问题

平时使用spectre仿真veriloga模型比较多,目前遇到过很多次收敛问题,也就是“ERROR (SPECTRE-16080): No DC solution found (no convergence). Last acceptable solution computed at 6.6 uA.”,在这里总结一下目前查到的 解决 方法。

(2025年回来看这个地方,想补充一下,就是我遇到的收敛问题大部分还是由于代码错误产生的。

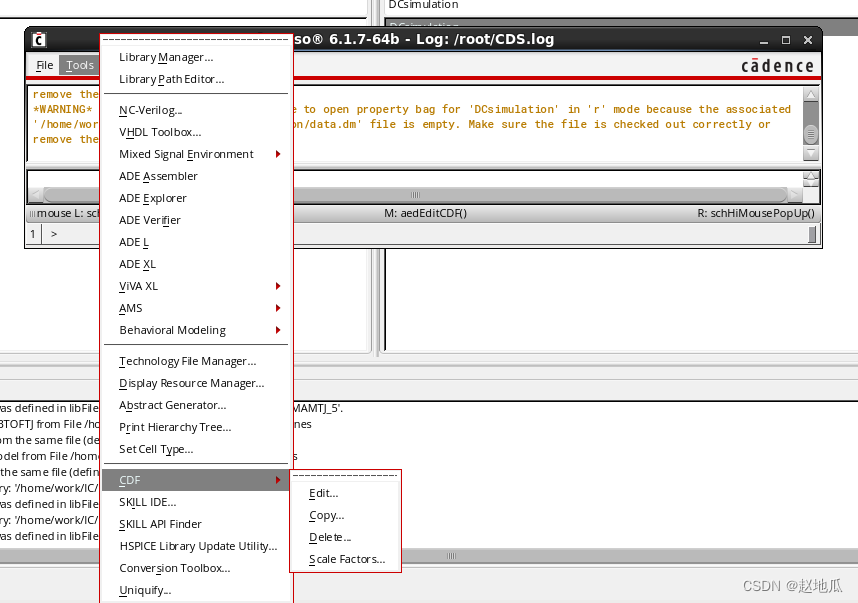

在veriloga模型里会定义一些parameter,每次在代码里修改就很麻烦,CDF(Component Description Format)提供了解决方法:通过tools-CDF-edit,选择“Base”作为变量 类 型,即可添加可供编辑的变量,然后在原理图中选中器件再按q,即可修改。

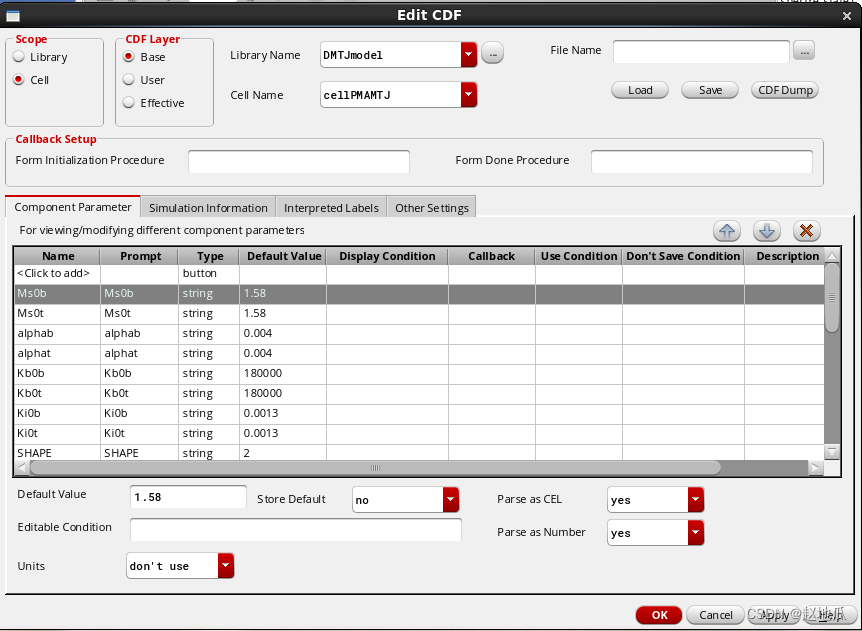

打开CDF edit界面如下:

简单记录一下在type为“srting”时,几种选项的含义:

Parse as CEL:仅用于string类型变量。

Parse as number:此属性仅用于 string 类型的变量包含数字的情况。

Store Defalt:默认情况下,Store default设置为"no"。

Defalt value:参数默认值,int、 float 、radio、cyclic和netset类型的参数必须具有默认值。如果未为这些类型的参数指定默认值,CIW中的错误消息将显示未指定默认值的参数列表。

Display Condition :确定此参数是否显示在显示CDF参数的表单中。

Editable Condition:确定是否可以在显示CDF参数的表单中编辑此参数。

Units:此属性仅用于字符串类型参数,且Parse as number为"Yes",单位属性必须是以下之一:resistance, capacitance, inductance, conductance, time, frequency, power, powerDB, lengthMetric, lengthEnglish, angle, voltage, current, or temperature.

在进行DCanalysis时遇到warning"WARNING (SPECTRE-16707): Only tran supports psfxl format, result of other analyses will be in psfbin format."

在ADE菜单中output-save all-output format中选择psf格式即可。

由于需要运行verilogA程序,在仿真结束后的画图环节基本每三张图闪退一次,尝试了扩大虚拟机内存,增加处理器,删掉无用驱动等都不行,所以干脆就不绘图了,直接计算器输出结果...

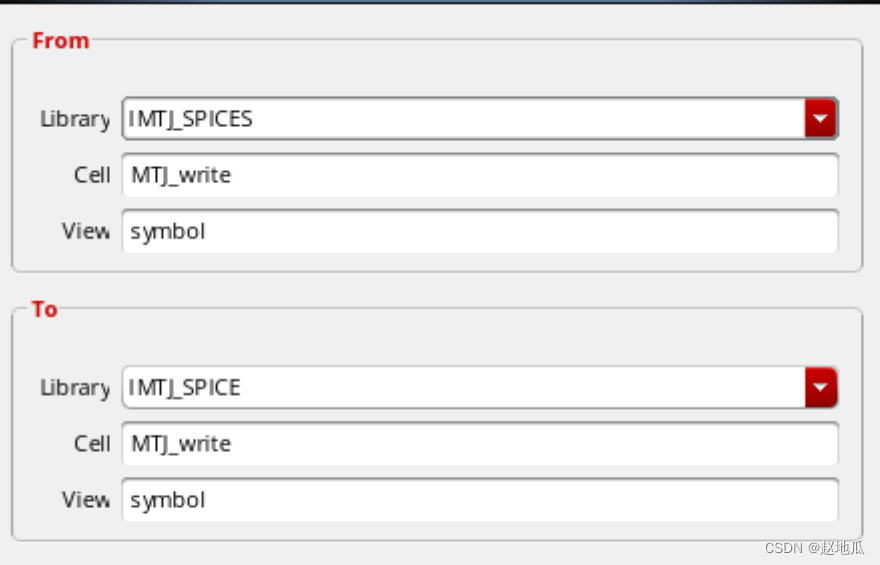

有时候在建新器件的时候不想重新画symbol,可以直接复制。

先右键需要被复制的symbol,选择copy,选择from... to...。

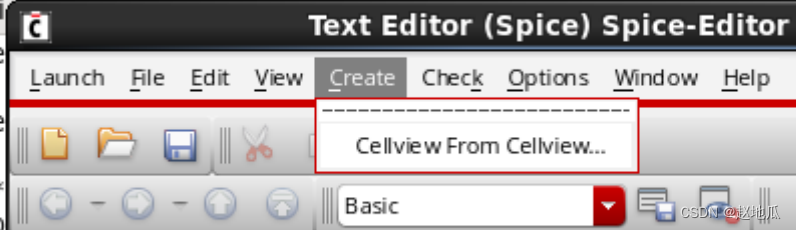

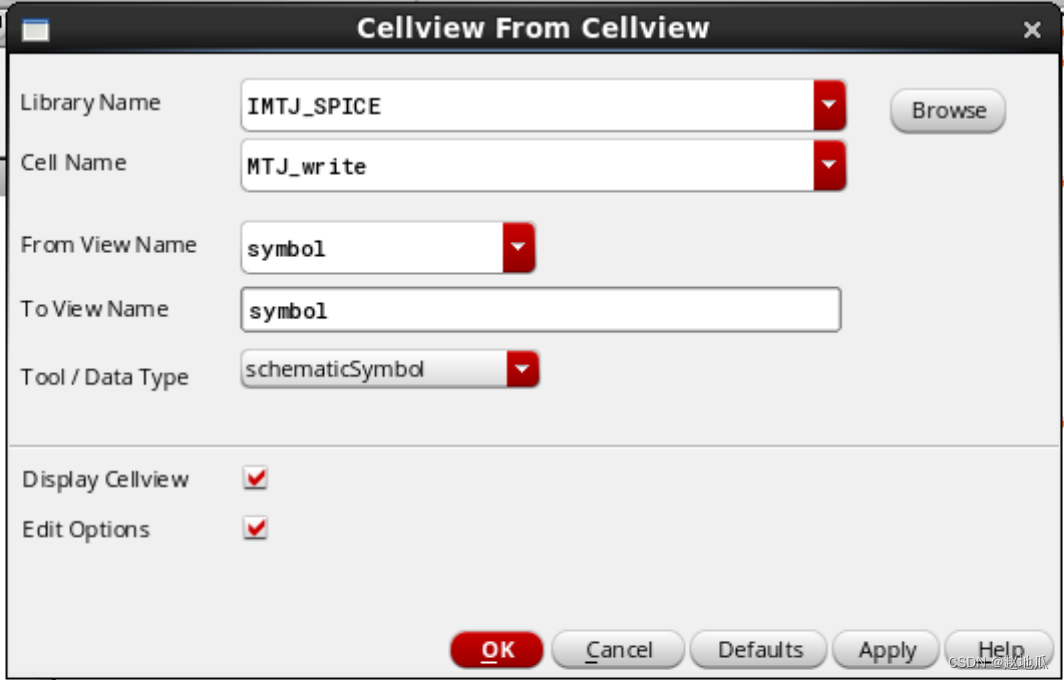

然后再从需要建立symbol的原理图或者代码上选择creat-cellview from cellview

最后选中刚复制过来的那个symbol-OK-modify就完成了。

【注意】要重新建立仿真文件,在这里一个疏忽又踩了大坑...

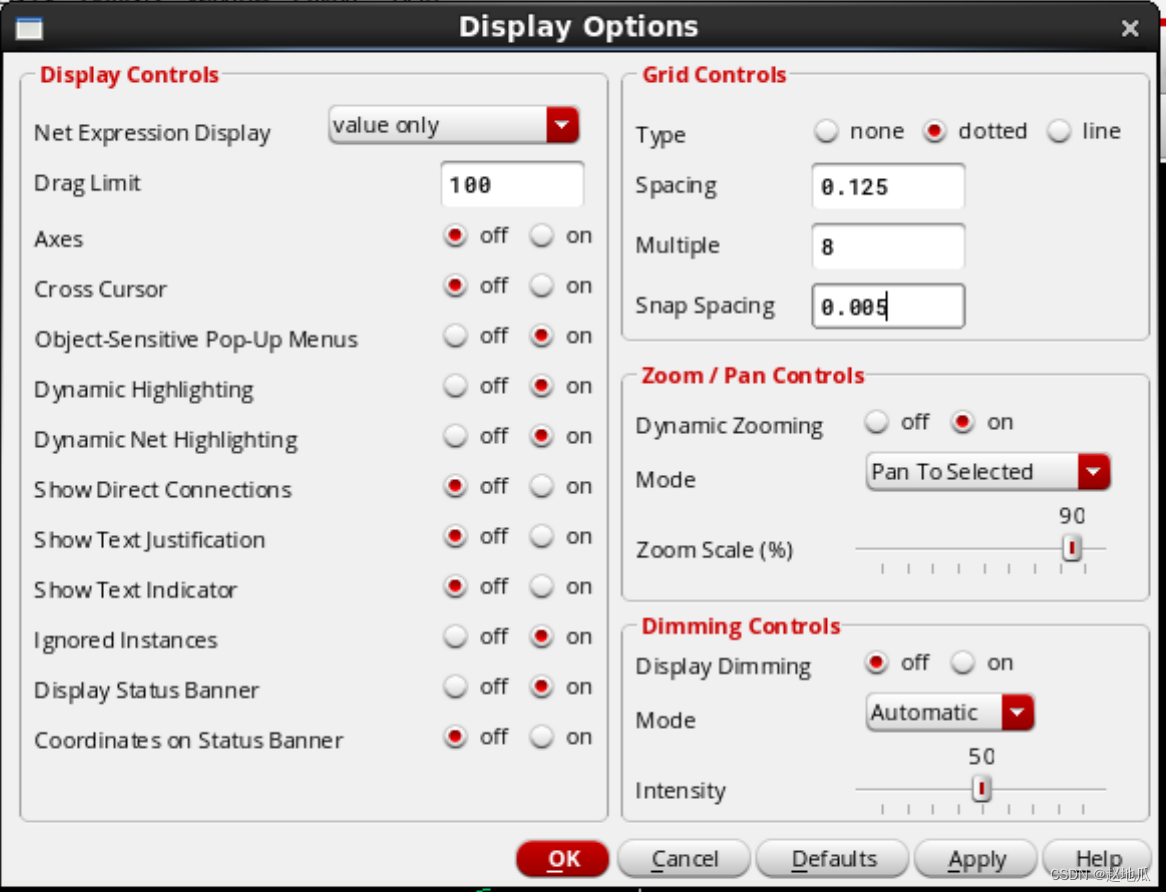

我在使用别人绘制的原理图时发现无法连接端口,解决方法参考:模拟IC设计中的软件操作:Cadence Virtuoso Schematic 电路原理图编辑技巧 - 哔哩哔哩 (bilibili.com)具体就是调节snap的spacing:

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删