今天和csdn同学讨论问题, 他说在他自己的实验库上添加了一个元件, 但是原理图中放置数据库元件时, 没看到自己新加入的元件.

他给了一段资料, 里面有如何添加CIS库元件的操作. 看了一下, 大家也都是这么添加元件, 没特别的.

可能就是他哪里少做了哪步引起的.

这里为他做个笔记, 描述如何在CIS库中添加新元件, 就用这位同学的实验库, 这就和他实验环境一模一样了(有利于他自己找缺了哪步).

自己的SPB17.4已经开始干正经活了, 先备份一下, 等给这位同学做完实验, 还要恢复到自己的工作环境.

备份和恢复自己的SPB17.4的步骤, 以前做过笔记cadence SPB(16.6 or 17.4) backup and restore , 就参考这篇笔记来备份.

看这些信息的目的: 看好路径后, 将这些路径中的内容都删了,

放入这位同学的实验库, 然后做实验, 就可以知道, 为啥这位同学说放了CIS库新元件, 但是原理图中没有这个元件的问题.

启动cadence服务

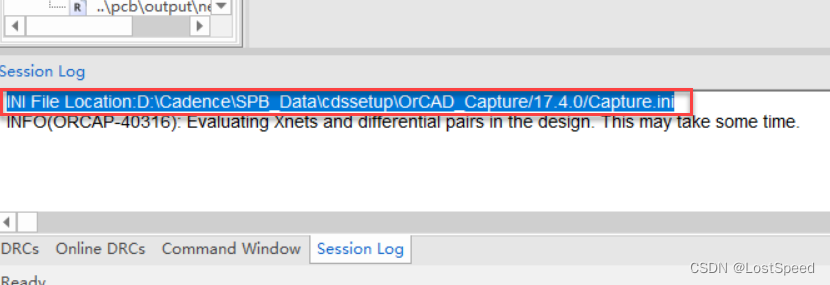

启动cadenceSPB17.4_Capture CIS 17.4, 在log窗口能看到ini的全路径名称

INI File Location:https://www.gofarlic.com\Cadence\SPB_Data\cdssetup\OrCAD_Capture/17.4.0/Capture.ini

打开Capture.ini, 找到原理图库配置的信息

[Part Library Directories]

Dir0=https://www.gofarlic.com\my_dev\my_local_git_prj\my_SPB_lib\sch_lib

[CIS Browse Directories]

Dir0=https://www.gofarlic.com\my_dev\my_local_git_prj\my_SPB_lib\datasheet

[Allegro Footprints]

Dir0=https://www.gofarlic.com\my_dev\my_local_git_prj\my_SPB_lib\pad_lib

Dir1=https://www.gofarlic.com\my_dev\my_local_git_prj\my_SPB_lib\pcb_lib

原理图库路径

https://www.gofarlic.com\my_dev\my_local_git_prj\my_SPB_lib\sch_lib

元件数据表的pdf路径

https://www.gofarlic.com\my_dev\my_local_git_prj\my_SPB_lib\datasheet

PCB库路径

https://www.gofarlic.com\my_dev\my_local_git_prj\my_SPB_lib\pcb_lib

焊盘库路径

https://www.gofarlic.com\my_dev\my_local_git_prj\my_SPB_lib\pad_lib

关掉所有已经打开的cadence SPB软件(orcad, allegro, viewer …), 停掉cadence 服务

删掉这4个目录中的所有东西

这4个目录, 我都做了git归档, 我就将这4个目录改个名字, 然后新建4个新目录出来做实验.

现在我已经有了4个空目录

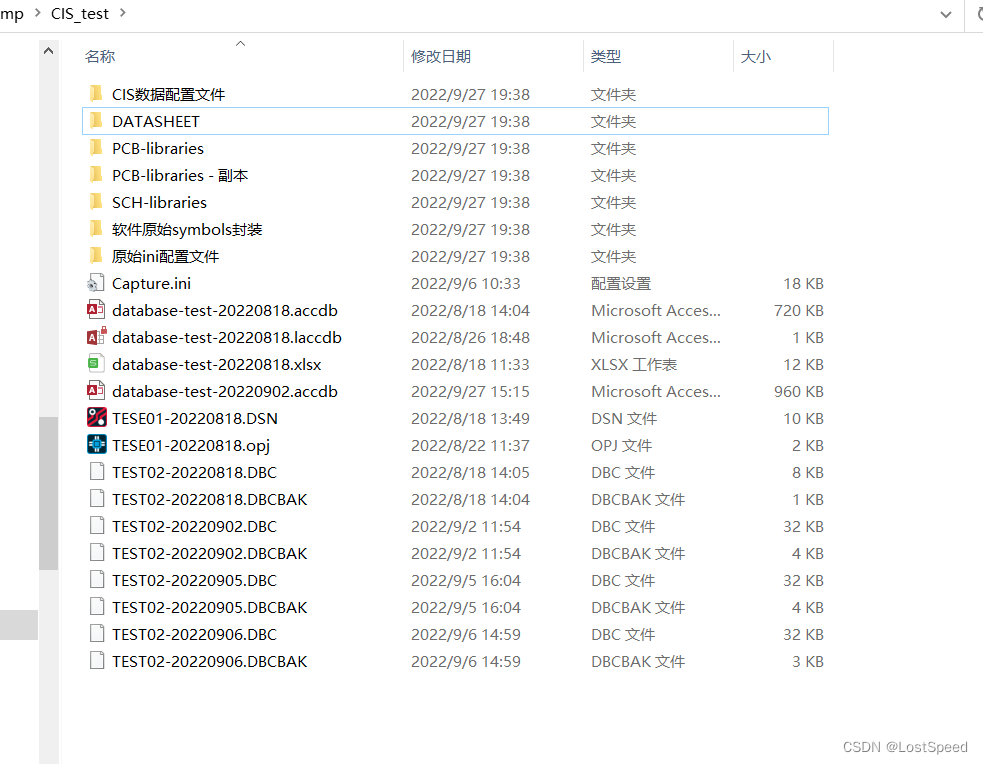

将csdn同学的压缩包解开如下

用csdn同学的测试库中的4个对应目录替换我建立的4个空目录的内容

https://www.gofarlic.com\my_dev\my_tmp\CIS_test\DATASHEET*.pdf => https://www.gofarlic.com\my_dev\my_local_git_prj\my_SPB_lib\datasheet

https://www.gofarlic.com\my_dev\my_tmp\CIS_test\SCH-libraries\*.olb => https://www.gofarlic.com\my_dev\my_local_git_prj\my_SPB_lib\sch_lib

https://www.gofarlic.com\my_dev\my_tmp\CIS_test\PCB-libraries\*.pad => https://www.gofarlic.com\my_dev\my_local_git_prj\my_SPB_lib\pad_lib

https://www.gofarlic.com\my_dev\my_tmp\CIS_test\PCB-libraries\*.dra => https://www.gofarlic.com\my_dev\my_local_git_prj\my_SPB_lib\pcb_lib

https://www.gofarlic.com\my_dev\my_tmp\CIS_test\PCB-libraries\*.psm => https://www.gofarlic.com\my_dev\my_local_git_prj\my_SPB_lib\pcb_lib

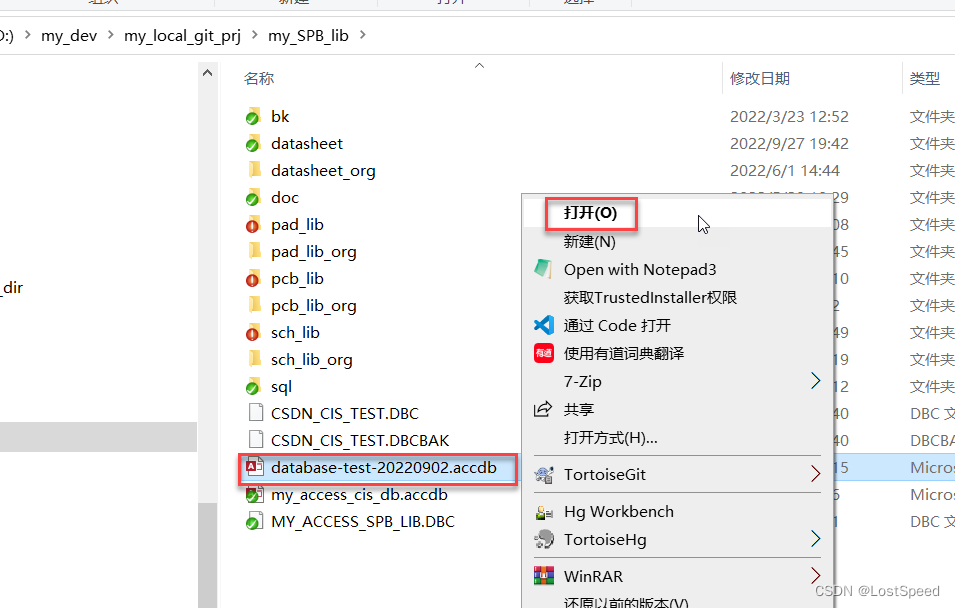

https://www.gofarlic.com\my_dev\my_tmp\CIS_test\database-test-20220902.accdb => https://www.gofarlic.com\my_dev\my_local_git_prj\my_SPB_lib

到这里, 我的实验环境就和csdn同学一样了

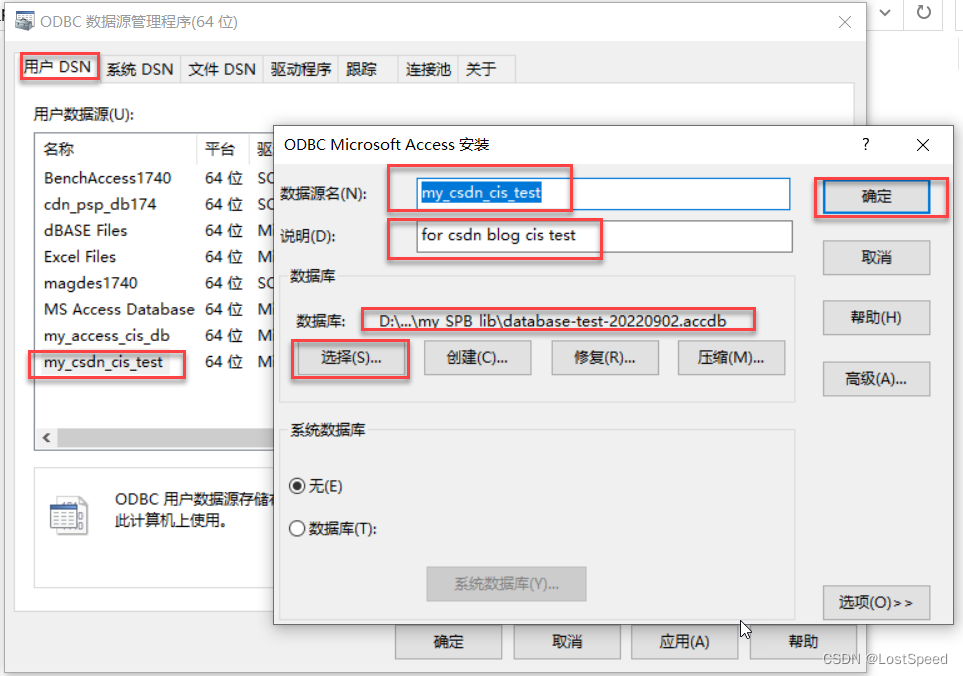

在ODBC数据源中为https://www.gofarlic.com\my_dev\my_local_git_prj\my_SPB_lib\database-test-20220902.accdb 建立一个ODBC连接

现在就有了一个可以在orcad中配置的CIS库的ODBC连接, 名称为my_csdn_cis_test

配置过程的细节可以参考笔记 cadence SPB17.4 part database

这里就记录一些不同点.

启动cadence服务

启动cadenceSPB17.4_Capture CIS 17.4

将 https://www.gofarlic.com\my_dev\my_tmp\CIS_test\TESE01-20220818.opj, TESE01-20220818.DSN 拷贝到 https://www.gofarlic.com\my_dev\my_tmp

打开https://www.gofarlic.com\my_dev\my_tmp\TESE01-20220818.opj

中间的配置过程就按照上面的笔记来, 没特别的.

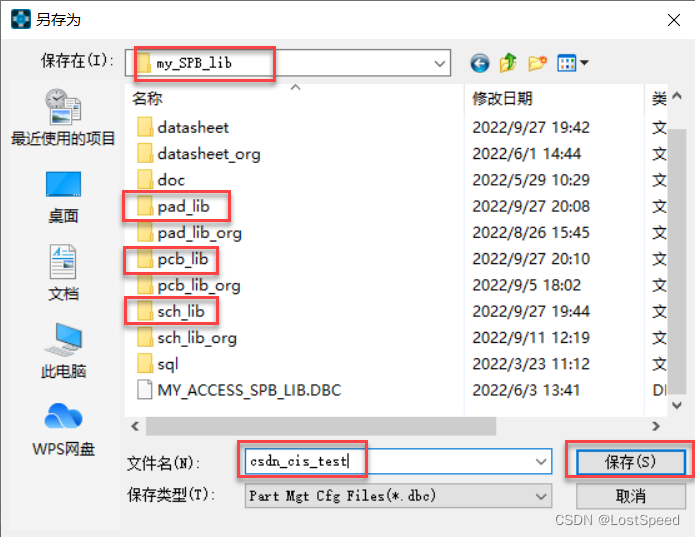

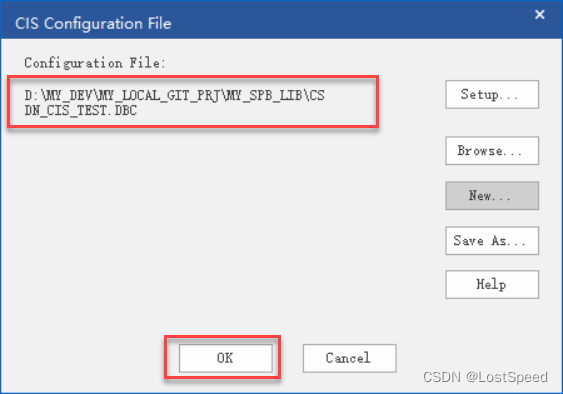

配置完后, 指定.dbc到 .accdb同级目录.

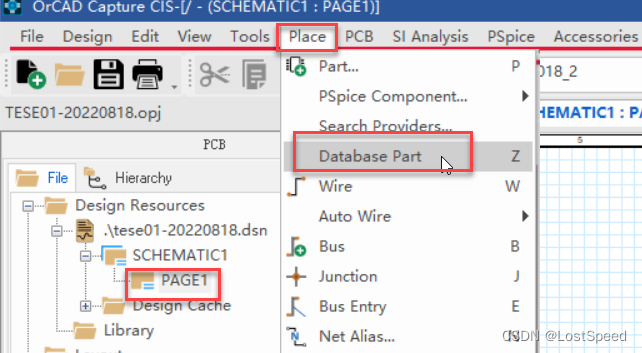

这位同学的库中, 已经有一些元件了, 先放一个数据库元件试试.

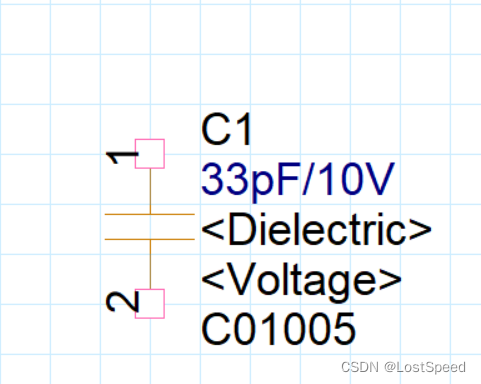

在原理图上, 出现了电容元件.

说明这位同学做的库是可用的.

假设就添加一个新电容吧.

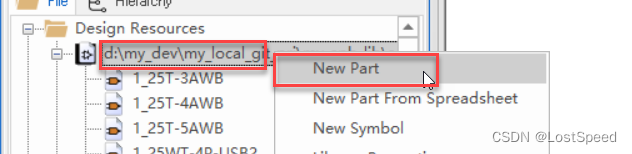

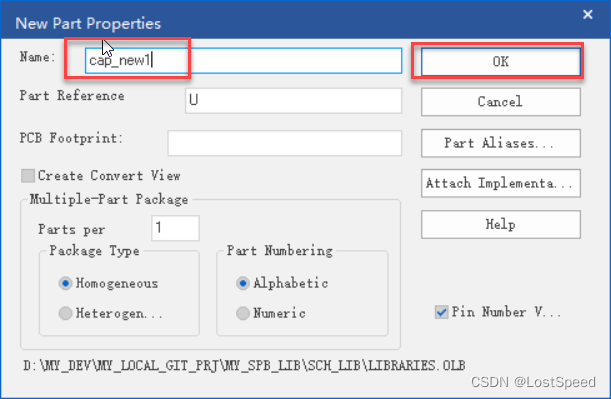

打开https://www.gofarlic.com\my_dev\my_local_git_prj\my_SPB_lib\sch_lib\LIBRARIES.OLB

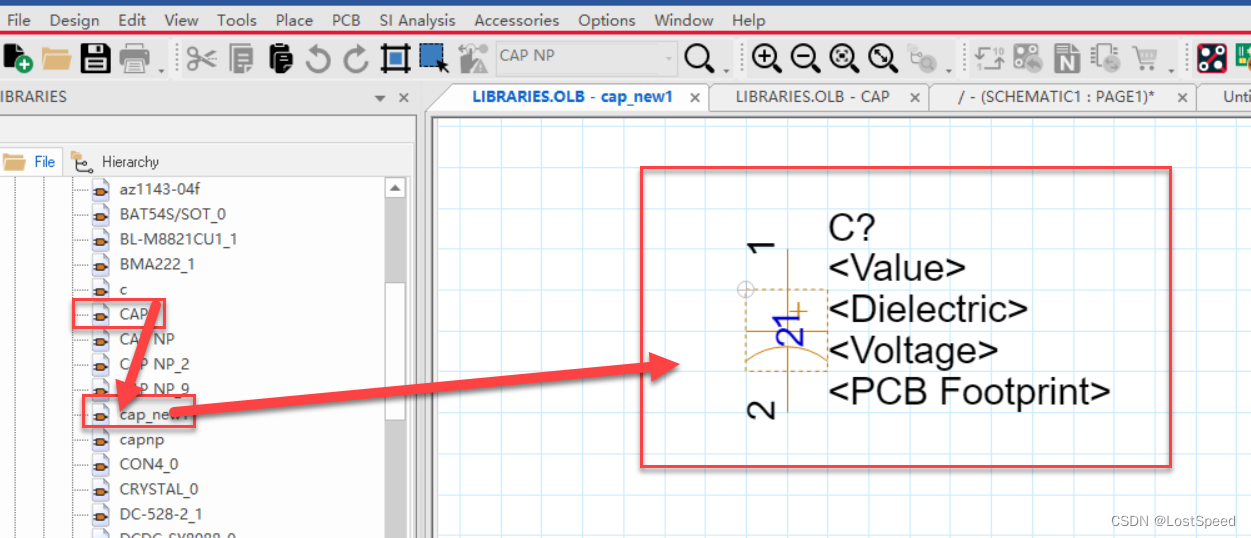

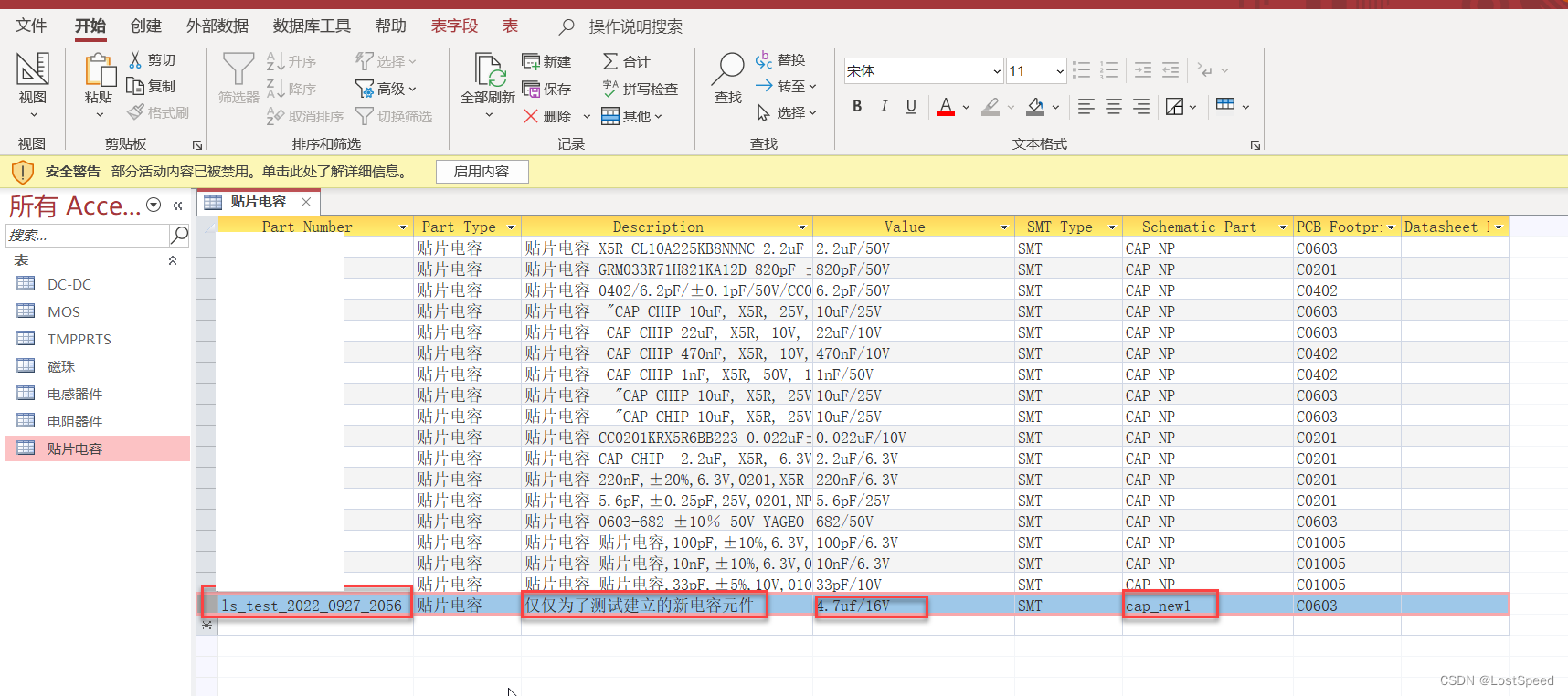

这个新元件 cap_new1, 我是从原理图库已经存在的元件 CAP 中拷贝过来的.

这样, 新元件 cap_new1就建立好了, 保存并关闭LIBRARIES.OLB

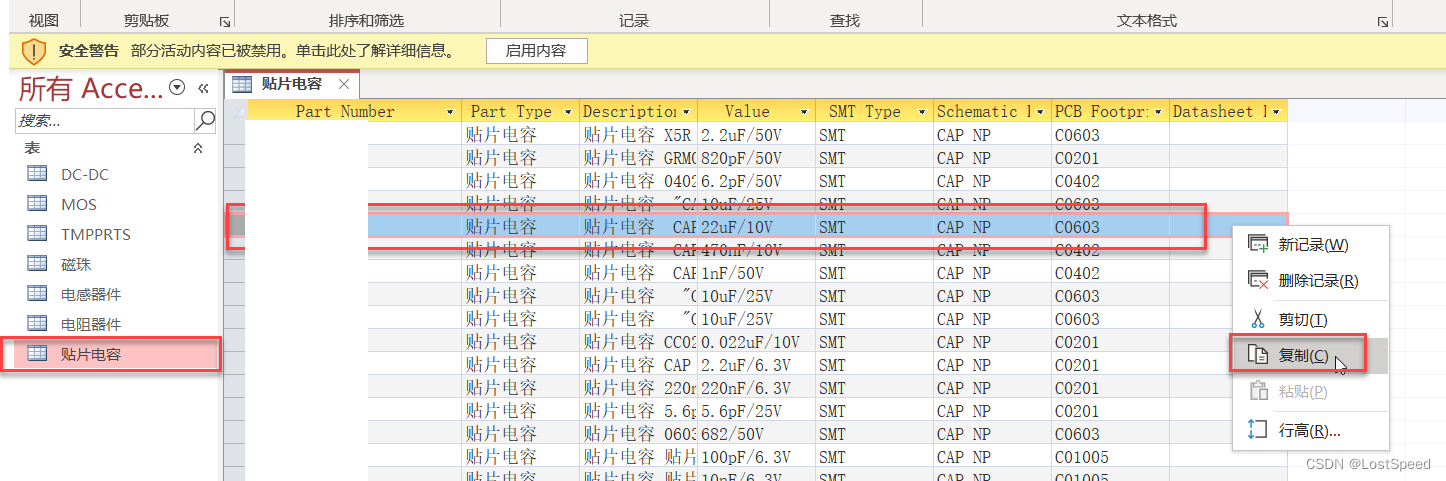

从0603电容上拷贝一行,粘贴到表尾部的新行, 然后改改, 将新元件填上.

保存并关闭 database-test-20220902.accdb

现在, 按理说, 在原理图中再放数据库元件时, 就应该有我们新做的这个cap_new1了.

来试试.

在修改库和mdb时, orcad capture CIS并没有关.

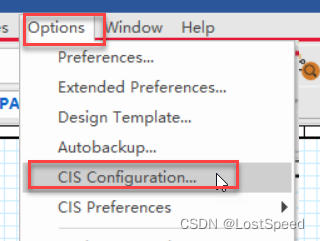

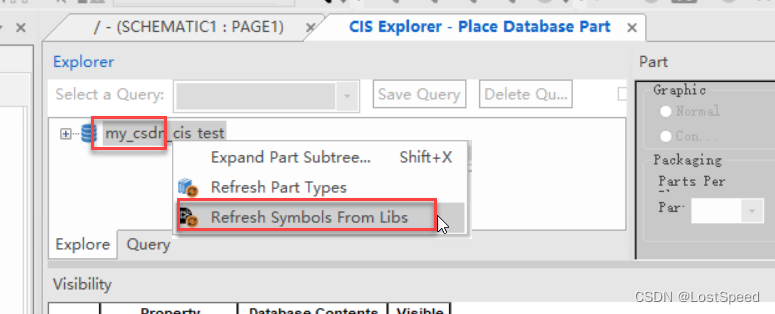

因为我们新加入了元件, 所以要让CIS先刷新一下.

我们只添加了新元件, 就刷新一下符号.

如果我们增加了新的元件 类 型, 就要点击第2项(“Refresh Part Types”), 来刷新提下元件类型.

如果你动了数据库, 不放心的话, 就将元件类型和符号都刷新一下.

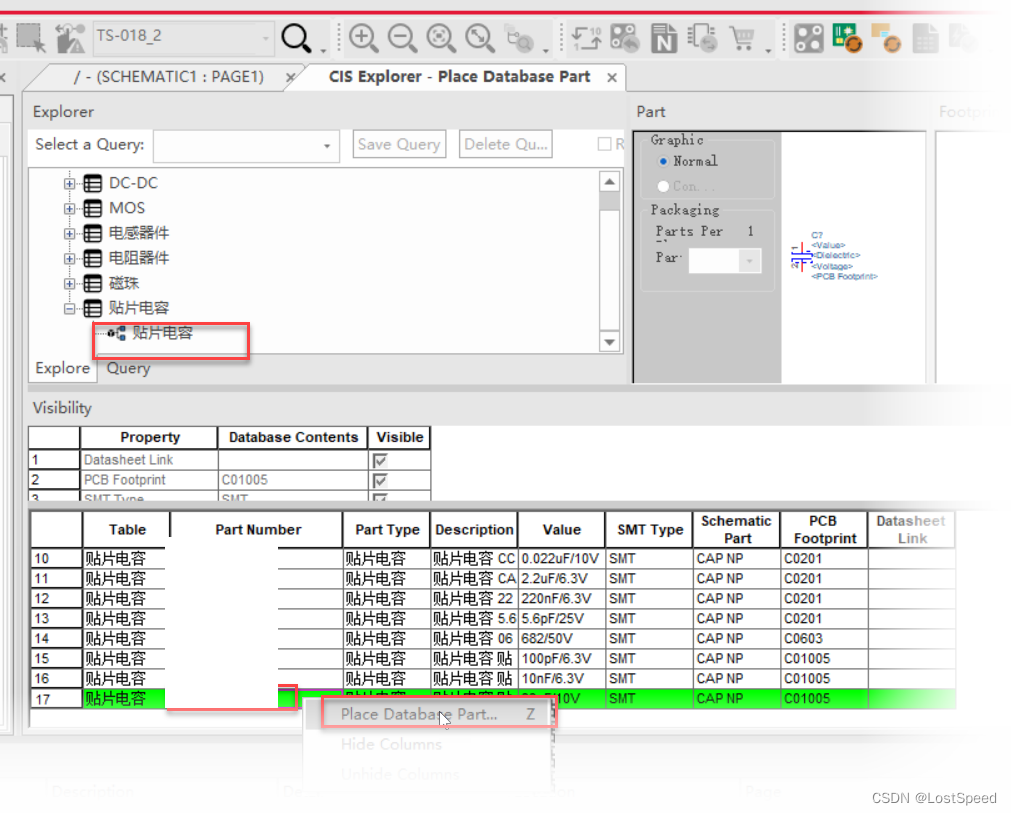

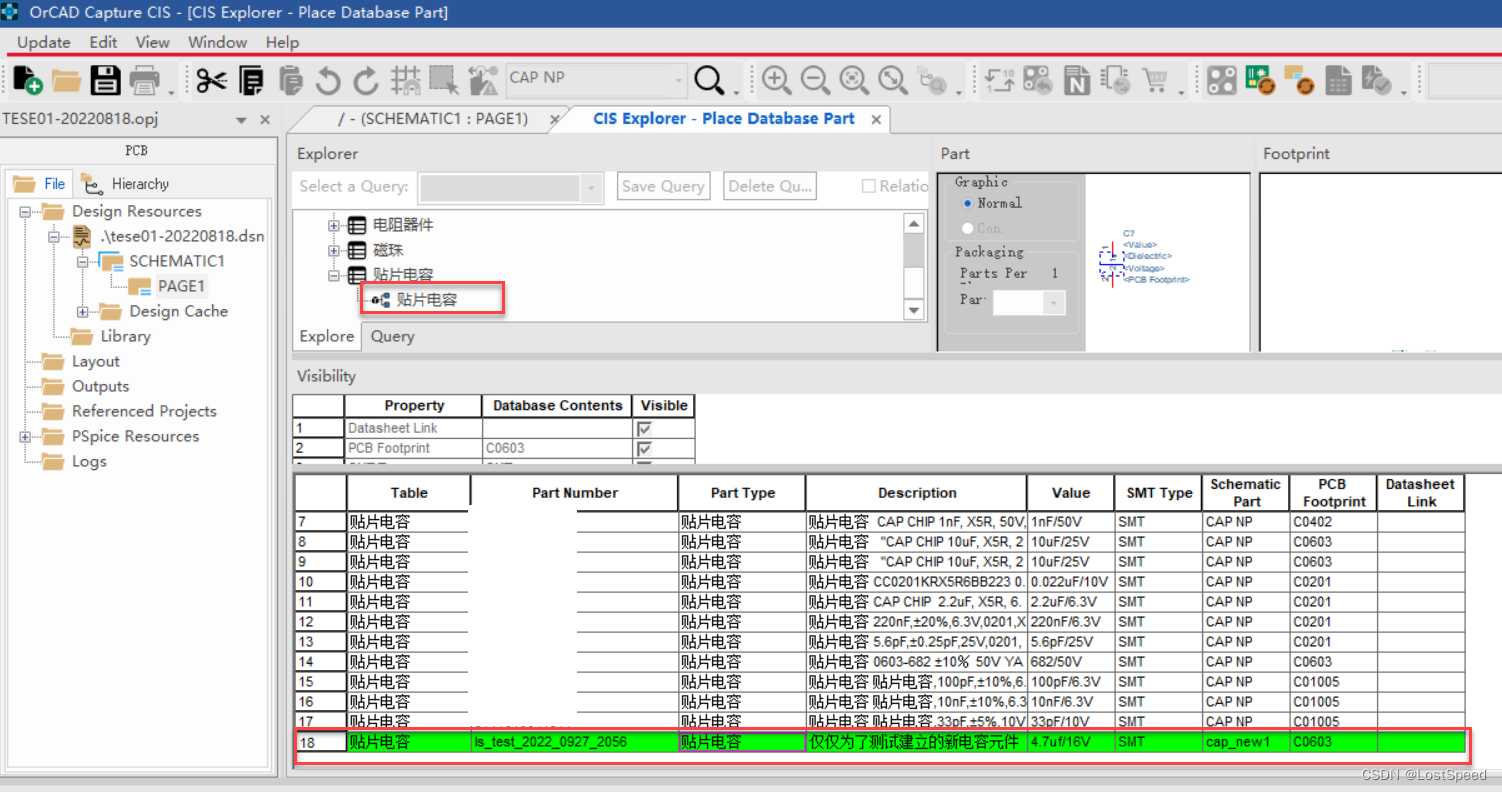

现在来浏览一下是否有我们新加的这个元件 cap_new1

可以看到, 我们通过2步增加的元件cap_new1, 是在贴片电容类别的最下面, 填的值, 也和我们改的MDB中的新元件登记信息一样.

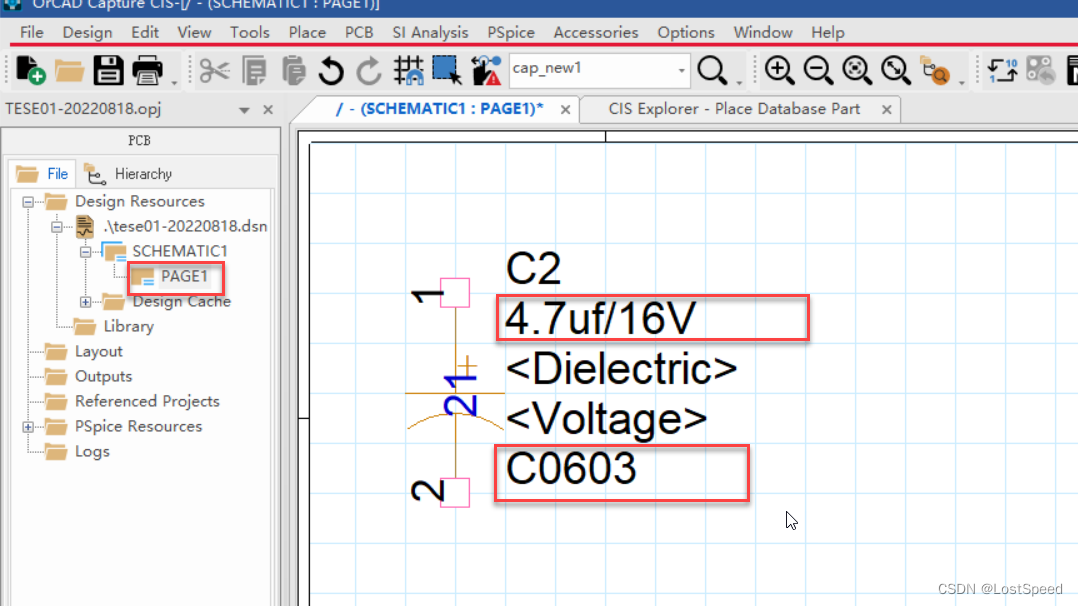

继续按Z键, 放置这个新元件cap_new1

可以看到, 放置我们新增的数据库元件 cap_new1成功.

做完了实验, 感觉和以前的操作(增加新元件, 编辑元件登记信息, 放置元件)都没有啥特别的地方.

这位同学说的不能放置新增的元件的情况, 我不能复现, 无法解决.

或者就是这位同学自己少做了哪步, 那就不太清楚了.

只能让他参照这个笔记, 自己去找找缺了哪步操作. 如果有啥问题, 只能再讨论了.

通过以上实验, 可以看出, 如果像这位同学这样的单数据库表, 要增加新元件的话, 只需要做3步:

免责声明:本文系网络转载或改编,未找到原创作者,版权归原作者所有。如涉及版权,请联系删